# embedded projects JOURNAL

OPEN SOURCE SOFT-AND HARDWARE PROJECTS

Eine Open-Source Zeitschrift zum Mitmachen!

# **PROTOTYPING**

#### [PROJECTS]

- Workshops in Augsburg

- PWM mit FPGA

- Ethernet für STM32F4 Discovery Board

- USB-CAN Adapter

- Vom Überweisungsauftrag zur TAN

- Distance Measurement

DAS HARDWARE FOR YOUR PROJECTS-PORTAL

Wussten Sie, dass wir eine Firma für kundenspezifische Entwicklungen mit Sitz in Augsburg sind?

#### Wir bieten:

Hardware, Software,

Embedded, SoftwareEntwicklung,

Mikrocontroller,

Anwendungsentwicklung,

Fachbeiträge/

Literatur, Schaltplan,

Webentwicklung,

Open-Source,

E-Commerce, Platinenlayout, GNU/Linux

Kommen Sie vorbei!

Holzbachstraße 4, D-86152 Augsburg Tel +49 (0) 821 279599-0 Fax +49 (0) 821 279599-20 info@embedded-projects.net [Editorial] Benedikt Sauter

### **Einleitung**

#### Ausgabe 04/2012

**Embedded Projects Journal - Ausgabe No. 15**

#### Einleitung \_

Wer rastet der rostet. Naja so alt sind wir jetzt auch nicht, aber Bewegung ist das, was allen gut tut. Wir schauen mit einem positiven Blick in das vergangene und ebenfalls mit einem positiven Blick in das neue Jahr. Viel hatten wir uns vorgenommen und auch einiges umgesetzt.

Aktuell freuen wir uns neue Sponsoren im Journal begrüßen zu dürfen. So haben wir Eurocircuits[1] als weiteren DIN A4 Sponsor im Boot. Und damit sich so ein Boot stabil im Wasser bewegt, müssen viele Positionen gut besetzt sein. Neben den zahlreichen freiwilligen Autoren, Lesern und Sponsoren gilt an dieser Stelle auch ein besonderer Dank dem Team rund ums Journal. Regelmäßig entsteht mit viel Arbeit und Fleiß eine komplette Ausgabe. Das sind immer 1 – 2 Wochen intensive Arbeit, bis so ein Heft in Form gegossen ist.

Kurz sei an dieser Stelle noch auf den Artikelwettbewerb[2] gemeinsam mit www.mi-krocontroller.net hingewiesen. Mikrocontroller.net veranstaltet mit dem embedded projects Journal zum zweiten Mal einen Artikelwettbewerb: Schreibe bis zum 1.3.2013 einen Artikel (im Artikelbreich bei mikrocontroller.net) über ein Elektronik- oder Embedded Systems-Thema, um am Wettbewerb teilzunehmen. Die besten Artikel werden prämiert und im embedded projects Journal veröffentlicht.

In diesem Sinne, Ahoi! Leinen los und auf nach 2013!

Benedikt Sauter

und das embedded projects Team!

- [1] http://www.eurocircuits.com

- [2] http://www.mikrocontroller.net

Hinweis: Zu jeden Artikel gibt es wieder einen Forumsbeitrag zur Diskussion

http://journal.embedded-projects.net/forum.php (Weiterleitung zu Mikrocontroller.net)

4/2012 JOURNAL - EMBEDDED-PROJECTS.NET

# →shop.embedded-projects.net

### HARDWARE FOR YOUR PROJECTS - ONLINESHOP

## Design your GNUBLIN

Sie suchen ein Board, das fast so wie GNUBLIN ist und brauchen davon nur eine kleine Menge pro Jahr? Wir passen Ihnen auf kurzem Weg die Schaltung an und ergänzen diese nach Ihrem Wunsch. Dank unserer internen Bestückung können wir Ihnen bereits ab kleinen Mengen ähnliche Stückpreise wie bei den GNUBLIN Boards in diesem Shop liefern.

www.gnublin.org/designer

### Die einfachste Möglichkeit an ein eigenes embedded GNU/Linux Board zu kommen!

Einfach und genial ist das Produkt "Design your GNUBLIN". Für alle, die kleine Serien von Platinen mit embedded GNU/Linux benötigen. Basierend auf der Schaltung der Boards der GNUBLIN Familie können wir einfach und schnell kundenspezifische Lösungen erstellen. Innerhalb kürzester Zeit können wir Ihnen die Boards von 1 bis ca. 1000 Stück liefern.

NEU:

online GNUBLINDesigner

mit Kalkulator

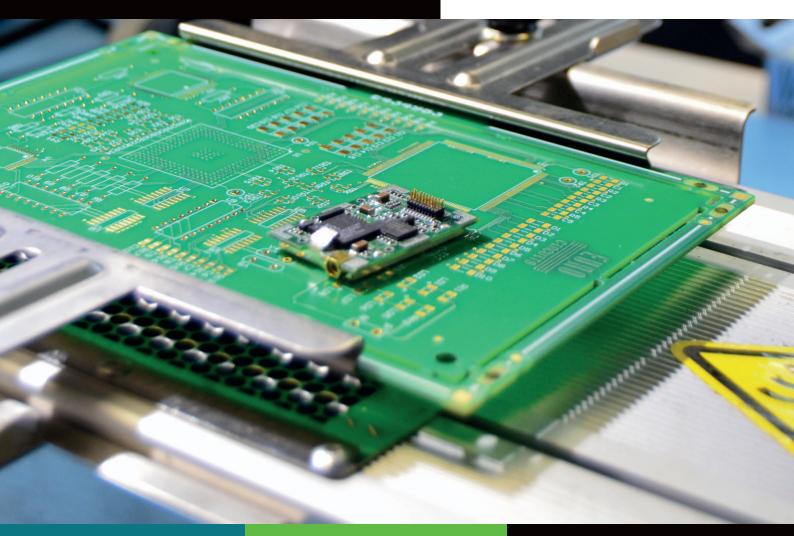

Wir zeichnen den Schaltplan und das Layout ...

... bestücken mit einem Automaten in Augsburg ...

... und nehmen die Schaltung für Sie in Betrieb.

Holzbachstraße 4, D-86152 Augsburg Tel +49 (0) 821 279599-0 Fax +49 (0) 821 279599-20 shop@embedded-projects.net

embedded projects GmbH

HARDWARE FOR PROJECTS

### Die Europäische Referenz für PCB Prototypen und Kleinserien

#### Kostensenkung durch Online-Pooling

- Keine Einrichtkosten

- Keine Mindesbestellwerte ab der 1. Platine

- Sofortbestellung Online ohne Vorkasse

#### Zeitgewinn durch Online-Daten-Check

- PCB Visualizer® Sofort Design-Rule-Check

- Online Tipps für DFM (Design-For-Manufacturability)

- Online-Optimierung mit Galvano-Simulation

#### PCB proto – spezieller Prototypen-Service für Entwickler, preiswert und schnell

- 1 oder 2 LP in 2, 3, 5 oder 7 Arbeitstagen

- DRC-geprüft, professionelle Ausführung inkl. 2x Lötstopplack und 1x Bestückungsdruck, 150µm Technologie

- 1 x 100 x 80mm in 7AT

- 2 Lagen 46.26 €

- 4 Lagen 93.94 €

- 2 x 100 x 80mm in 7AT

- 2 Lagen 36.28 € je LP 4 Lagen 73.52 € je LP

Preise inkl. 19% MwSt und ohne Transportkosten

#### STANDARD pool – die größte Auswahl an Eurocircuits Pooling Optionen

- 1-8 Lagen 150µm Technologie-Leiterplatten

- ab 2 AT

#### TECH pool – 100µm-Technologie mit allen Pooling-Vorteilen

- 2-8 Lagen 100µm Technologie-Leiterplatten

- ab 4 AT

#### IMS pool – Aluminiumkern-Leiterplatten für hohe Wärmeableitung (z.B. LED-Anwendung)

- Leiterplatten mit einlagig isoliertem Metallsubstrat

- ab 3 AT

#### On demand – Alle Optionen im Nicht-Pooling für Spezialanwendungen

- 1-16 Lagen bis 90µm-Technologie

- ab 2 AT

### **Workshops in Augsburg**

Benedikt Sauter <sauter@embedded-projects.net>

Wer kennt diesen Satz nicht: "Das wollte ich schon lange mal gemacht haben..."

... aber es ist schließlich nicht ganz so einfach, verschiedene Projekte im Alltag oder in der Freizeit unterzubringen. Ganz in diesem Sinne präsentiert unser Journal regelmäßig neue Themen und verschafft so den Einblick auf den Schreibtisch anderer Entwickler. Neu zum Journal kamen Ende 2012 zum ersten Mal auch Workshops bei uns in Augsburg hinzu.

Die Idee hatten wir schon länger und immer wieder mal in unseren Köpfen, nur gab es nie den richtigen Anstoß. Diesen hat uns schließlich die Firma Eurocircuits [1] aus Belgien geben. "Habt Ihr nicht Lust, gemeinsam mit uns einen Workshop über das Bestücken von SMD-Platinen anzubieten?"

An dieser Stelle ein großer Dank an Uwe Dörr :)

Es hat richtig Spaß gemacht!

bedruckt, von Hand bestückt und im

4/2012 JOURNAL - EMBEDDED-PROJECTS NET

Was braucht man um einen Workshop anbieten zu können? Einen passenden Raum, genügend Tische und Stühle, zwischendrin etwas zum Essen für die Bäuche und natürlich genügend Kaffee und Getränke – alles machbar.

Die ersten beiden Workshops gemeinsam mit Eurocircuits waren ein voller Erfolg. Aufgrund der vielen Anmeldungen für den Workshop SMD-Bestückung mussten wir gleich einen zweiten Termin am Tag darauf öffnen; sonst wäre alles aus den Nähten geplatzt. Ebenfalls war der Eagle-Kurs so schnell voll, wie wir alle gar nicht schauen konnten.

- SMD Bestückung von Platinen

- Die Neuerungen bei Eagle 6.0 / Bibliotheken anlegen mit Eagle

Wir sind also bereit für die nächsten Termine:

- 06.02.2013 Arbeiten mit dem Platinen-Layout Programm Eagle (Richard Hammerl)

- 13.03.2013 embedded GNU/Linux als Mikrocontroller-Ersatz (Benedikt Sauter)

In Zukunft wollen wir zu den eurocircuits Workshops auch eigene bzw. auf Wunsch von Lesern, Kunden, Entwicklern aktuelle Themen aufsetzten und uns dort einen passenden Experten holen. Für Wünsche, Anregungen etc. sind wir wie immer offen. Es soll ein Mix aus kostenlosen und optional auch intensiveren kostenpflichtigen Schulungen (ggf. mit Material) werden.

Für die Schulungen haben wir daher eine Internetseite [2] eingerichtet, auf der man die Termine und Anmeldeformulare findet.

In diesem Sinne freuen wir uns auf viele weitere nette Gespräche und Themen.

- [1] http://www.eurocircuits.com

- [2] http://schulungen.embedded-projects.net

#### Nächste Termine:

6.2.2013 Arbeiten mit dem Platinen-Layout Programm Eagle (Richard Hammerl)

13.03.2013 embedded GNU/Linux als Mikrocontroller-Ersatz (Benedikt Sauter)

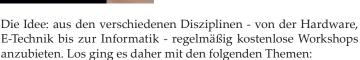

### **PWM** mit FPGA

#### Christian Kähler <kaehler.christian@gmx.net>

#### **Einleitung**

Im Rahmen einer Lehrveranstaltung an der Hochschule Merseburg (FH) ist dieses Projekt im Sommersemester 2012 entstanden. Ziel

ist es, einen handelsüblichen PWM-Lüfter aus dem PC-Sektor mit einem FPGA anzusteuern und dessen aktuelle Drehzahl auszulesen (siehe Abb 1). Das Ganze soll dahingehend weiterentwickelt werden, dass die Drehzahl automatisch in Abhängigkeit von Temperaturen geregelt wird. Dieser Artikel soll zeigen, wie ein PWM-Lüfter manuell über Taster gesteuert werden kann. Es ist natürlich möglich, das Ganze auf die Steuerung mehrerer Lüfter auszuweiten. Die Projektdateien und auch eine ausführlichere Beschreibung des Projektes sind zu finden unter:

http://www.hs-merseburg.de/~8ckaehle/master/projekt\_PWM\_Luefter.htm

#### Spezifikation der elektrischen Anforderungen

gung PWM-Lüfter

U [V] gung: t [µs]

Abb. 3: PWM-Signal

Für den Umgang mit PWM-gesteuerten Lüftern gibt es besondere Spezifikationen, welche von Intel unter [1] veröffentlicht wurden. Diese stellen einen Standard dar. Handelsübliche Lüfter aus dem PC-Sektor müssen mit einer Versorgungsspannung von 12 V versorgt werden [vgl. 1, S.9]. Der standardisierte Steckverbinder ist

vierpolig. Abbildung 2 zeigt den Stecker eines PWM Lüfters mit folgender Pinbele-

> Pin1 - PWM-Eingang ; Pin2 - Tachosignal; Pin3 - +12V ; Pin4 - GND

Die Drehzahl des Lüfters ist proportional zu einem zu erzeugenden PWM-Signal. Hierbei hängt die Drehzahl von der Pulsbreite ab. Nominal ist eine Frequenz zwischen 22kHz und 28kHz zu erzeugen. Pro Umdrehung liefert der Lüfter zwei Pulse, die zur Erkennung der aktuellen Drehzahl ausgewertet werden können. Beim Tachosignalausgang handelt es sich um eine Open-Collector beziehungsweise eine Open-Drain Schaltung. Es ist daher zwingend ein Pullup-Widerstand vorzusehen [vgl. 1, S.9]. Abbildung 3 zeigt eine Periode des zu erzeugenden PWM-Signals. Für das Projekt ist wichtig, die Periodendauer T auf 40µs festzusetzen. Dies entspricht einer Frequenz von 25kHz. Die Länge des Pulses  $\tau$  ist hierbei variabel. Aus den beiden Werten lässt sich der Duty Cycle berechnen, welcher die eigentlich wichtige Größe zur Steuerung der Drehzahl des Lüfters darstellt.

$(DC = \tau T * 100)$

#### Generierung eines PWM-Signals aus dem Systemtakt

Für die Geschwindigkeitsregelung ist die direkte Steuerung der Pulsbreite des PWM-Signals vorgesehen. Der Duty Cylcle kann hierbei mittels Taster zwischen 30 % und 80 % in 5%-Schritten eingestellt werden. Die Erzeugung des Signals erfolgt durch eine Teilung des 50 MHz Systemtakts auf einen 25 kHz PWM-Takt mit variabler Einstellung der Pulsbreite. In der Architektur der entity "pwm" (pwm.vhd) existieren zwei unabhängige, parallel laufende Prozesse. Der erste Prozess nimmt die Nutzereingaben entgegen und verändert die Pulsbreite des PWM-Signals. Der zweite Prozess sorgt für die Ausgabe des PWM-Signals und für die Ansteuerung der LED-Leiste.

Die Ableitung des benötigten Takts soll durch einfaches Zählen der Flanken des Systemtakts realisiert werden. Im Voraus ist der erforderliche Maximalwert des Zählers nach folgender Vorschrift zu berechnen:

1 s50000000 [Schritte]=40 µsx [Schritte] -> x=40\*10-6\*50\*106 =2000

Hieraus ergibt sich, dass ein Zähler bei einem 50MHz Takt genau 40µs benötigt um den errechneten Maximalwert von 2000 zu erreichen. Dies spiegelt die gewünschte Periodendauer direkt wider. Um ein PWM-Signal zu erzeugen, muss

auf dem Ausgang, in diesem Fall der Port "pwm\_out", für eine definierte Zeit ein High-Signal ausgegeben werden.

Wie bereits erläutert, wird zur direkten Steuerung der Geschwindigkeit nur der Duty Cycle verändert. Der erste Prozess der entity "pwm" (pwm.vhd Zeile 25-38) realisiert genau das, über einen vom Benutzer bedienbaren Taster. Der Prozess "pwm\_einstellung" reagiert hierbei auf eine fallende Flanke des Tasters (pwm. vhd Zeile 28). Eine fallende Flanke signalisiert das Drücken des Tasters, da diese auf dem verwendeten DE0 Board LOW-Aktiv angebunden sind Erste praktische Versuche am verwendeten Lüfter zeigten, dass keine Geschwindigkeitserhöhung ab einem Duty Cycle von 80% stattfinden. Daher wurde der maximale Duty Cycle auf 80% begrenzt. Dies entspricht einem Zählerwert von 1600. Die Einstellung des neuen Duty Cycles erfolgt durch eine einfache Abfrage (pwm.vhd, Zeilen 29-33). Ist der aktuelle Duty Cycle beziehungsweise Zählerwert kleiner als das Maximum, wird der aktuelle Zählerstand um 100 erhöht. Dies entspricht einer Erhöhung des Duty Cycles um 5%. Ist der Maximalwert erreicht, wird der Duty Cycle auf den Wert 30% zurückgesetzt. Dies entspricht einem Zählerwert von 600. Der aktuelle Wert des Duty Cyc-

les wird in einem weiteren Prozess direkt zur Ausgabe des PWM-Signals genutzt. Der Prozess "pwm-ausgabe" (pwm.vhd, Zeilen 44-80) teilt sich in zwei Vorgänge. Als erstes wird anhand des im Prozess "pwm\_einstellung" eingestellten Duty Cycles ein LED-Vektor angesteuert, um die aktuelle Einstellung für den Benutzer sichtbar zu machen. In einem zweiten Schritt wird das PWM-Signal erzeugt. Das Signal "pwm\_HIGH" wird hierbei direkt genutzt, um zu bestimmen, für wie viele Zählschritte das Ausgangssignal einen High-Pegel führen soll. Mit einer einfachen Case-Anweisung wird entschieden, wie viele der zehn LEDs in Abhängigkeit von der Länge der Pulsbreite leuchten sollen (pwm.vhd, Zeilen 46-60). Die eigentliche Erzeugung des PWM-Signals realisiert der zweite Teil des Prozesses (pwm.vhd, Zeilen 63 – 74).

### Generierung eines PWM-Signals aus dem Systemtakt

Für die Detektion und Auswertung des Tachosignals sind mehrere Prozesse und Blöcke notwendig. Wie bereits erläutert, liefert der Lüfter für jede Umdrehung zwei Pulse. Diese können für die Auswertung gezählt werden. Um eine Berechnung der Umdrehungen pro Minute zu ermöglichen, ist eine definierte Messzeit sicherzustellen. In diesem Fall bietet es sich an, die Pulse eine Sekunde lang zu zählen, da hierdurch leicht eine Umrechnung auf die Umdrehungszahl pro Minute ermöglicht wird. Für die Erzeugung eines Pulses pro Sekunde ist ein einfacher Zähler ausreichend. Der Zähler inkrementiert seinen Wert im Bereich von 0 – 49999999 bei jeder steigenden Flanke des Systemtakts (sek\_count.vhd, Zeilen 20-25). Erreicht der Zähler einen Stand von 49999999, gibt er ein Flag aus, welches

das Erreichen einer Sekunde signalisiert (sek\_count.vhd, Zeilen 26-28). Anhand dieses Flags kann die Auswertung angestoßen werden. Durch den Auswertungsprozess wird das Erkennen dieses Flags bestätigt, wodurch der Zähler auf seinen Minimalwert zurückgesetzt wird (sek\_count.vhd, Zeilen 21-23). Die eigentliche Auswertung und Anzeige des Tachosignals realisieren zwei weitere Prozesse, welche in ei-

```

35 ⊟tacho_zaehl: process (clk50MHz ,tacho_in)

36 | --variable mittelung : integer range 0 to 10 :=0;

37 | begin

39 □ if (rising_edge(clk50MHz)) then

40 | flanke(1)<=flanke(0);

41 | flanke(1)<=flanke(0);

42 | if (flanke = "10" and flag = '0') then

44 | count <= count + 1;

45 | cnt_temp <= count+1;

46 | end if;

47 | if flag = '1' then

49 | count <= 0;

49 | end if;

50 | end if;

51 | end process tacho_zaehl;

Abb. 6: Tacho VHD Teil 1

```

nem Block enthalten sind. Die entity "tacho" (tacho.vhd) enthält einen Prozess, der die Pulse zählt und nach einer Zählzeit von einer Sekunde die Umrechnung in die Umdrehungszahl pro Minute anstößt. Ein zweiter Prozess in dieser Architektur führt die Berechnung und die Ausgabe der aktuellen Umdrehungszahl durch. Die Pulse werden mit einer Abtastfrequenz von 50 MHz, also dem Systemtakt, gezählt (tacho.vhd, Zeile 39). Da innerhalb eines Prozesses nur auf die Flanken eines Signales getriggert werden kann, muss die Erfassung der Pulsflanken des Lüfters durch eine andere Methode realisiert werden. Ein einfaches zwei Bit breites Schieberegister eignet sich hier in besonderem Maße (tacho.vhd, Zeilen 40-41). Wird eine Flanke erkannt (flanke = "10") und die Messzeit einer Sekunde ist noch nicht erreicht (flag = 0), wird der Pulszähler "count" inkrementiert (tacho.vhd, Zeile 43-45). Ist die maximale Messzeit erreicht (flag = 1), wird der Zähler zurückgesetzt und die Auswertung angestoßen. Zu jeder steigenden Flanke des Systemtaktes wird zunächst das Clear-Signal zurückgesetzt (tacho.vhd, Zeile 63/64). Wird dieses Signal gesetzt, wird der Sekundenzähler zurückgesetzt (sek\_count.vhd, Zeile 21) und somit die Fertigstellung der Verarbeitung signalisiert. Führt das Signal "flag" des Sekundenzählers einen High-Pegel, muss die Verarbeitung der gemessenen Pulsflanken gestartet werden (tacho.vhd, Zeile 65). Für die Umrechnung der in einer Sekunde gezählten Pulse in die Umdrehungszahl pro Minute wird folgende Beziehung verwendet:

Abb. 4: VHD Teil 1

```

pwm ausgabe: process (clk50MHz, reset)

begin if (rising_edge(clk50mhz)) then

45

46

47

48

case pwm HIGH is

49

then 600 => led_vector <="0000000000";

when 700 => led_vector <="1000000000";

when 800 => led_vector <="1100000000";

when 900 => led_vector <="1110000000";</pre>

51

52

53

when 1000 => led_vector <="1111000000";

when 1100 => led_vector <="1111100000";

54

55

when 1200 => led_vector <="1111110000";

when 1300 => led_vector <="1111111000";

56

57

when 1400 => led_vector <="11111111100";

when 1500 => led_vector <="11111111110";

58

when 1600 => led vector <="1111111111";

60

61

62

when others => led_vector <= "0000000000";

end case;

63

64

if reset = '0' then

65

66

67

68

69

70

71

pwm_out <= '0';

else

if (count1 < (PWM freq - PWM HIGH)) then

pwm out <= '0';

count1 <= count1 + 1;

elsif (count1 < (PWM_freq)-1) then

pwm_out <= '1';

count1 <= count1 + 1;

72

73

74

75

76

77

78

count1 <= 0;

end if:

end if:

79

nd process pwm_ausgabe;

end rtl;

```

#### Abb. 5: VHD Teil 2

```

= tacho_auswert : process (clk50MHz,flag)

56

variable wert : integer range 0 to 9000;

variable temp : integer;

variable tausender : integer range 0 to 9;

58

59

60

variable hunderter : integer range 0 to 9;

variable zehner : integer range 0 to 9;

61

variable einer

: integer range 0 to 9;

62

begin

if (rising_edge(clk50MHz) ) then

clear <= '0';

if flag = '1' then</pre>

63

64

65

66

67

ticks in rpm umrechnen

wert := (cnt temp * 30);

if ((cnt_temp*30) < 200) then alarm_out <= '1';

山上回

68

69

70

71

else

alarm_out <= '0';

72

73

74

Einerstelle extrahieren

einer := temp;

- Zehnerstelle extrahieren

wert := wert - temp;

temp := wert mod 100;

zehner := temp / 10;

-- Hunderterstelle extrahieren

wert := wert - temp;

temp := wert mod 1000;

hunderter := temp / 100;

-- Tausenderstelle extrahieren

wert := wert - temp;

temp := wert mod 10000;

90

tausender := temp / 1000;

clear <= '1';

end if;

ein <= conv_std_logic_vector(einer, 4);

zehn <= conv_std_logic_vector(zehner, 4);</pre>

hundert <= conv_std_logic_vector(hunderter, 4);

tausend <= conv_std_logic_vector(tausender, 4)

end process tacho auswert;

```

Abb. 6: Tacho VHD Teil 2

In der VHDL-Beschreibung findet sich der errechnete Wert schlussendlich in der Variable "wert" (tacho.vhd, Zeile 67). In einem ersten Schritt wird überprüft, ob die aktuelle Drehzahl sich in einem kritischen Bereich befindet. Kritisch wird hierbei als "Umdre-

hungen < 200" definiert. Ist dies der Fall, wird ein Flag gesetzt, welches in einem weiteren Prozess einen Piezosummer als Alarmgeber ansteuert (tacho.vhd, Zeilen 68-71). Durch die Berechnung (tacho.vhd, Zeile 67) entsteht ein vierstelliger Dezimalwert. Da dieser nicht ohne weitere Umformung auf den Sieben-Segment-Anzeigen ausgegeben werden kann, bedarf es einer weiteren Umformung. Mittels Modulo-Operatoren wird die jeweilige Stelle aus der Dezimalzahl extrahiert (tacho.vhd, Zeilen 74-92). Abgeschlossen wird die Verarbeitung mit der Signalisierung für den Sekundentimer (clear = 1).

#### Literatur

[1] Intel Corporation (2005): 4-Wire Pulse Width Modulation (PWM) Controlled Fans – Specification – Revision 1.3 Online im Internet. URL: http:// formfactors.org/developer/ specs/4\_Wire\_PWM\_Spec.pdf (Abruf: 12.04.2012)

ICnova i.MX536 SODIMM

High End Cortex-A8 SODIMM-200 Modul

WWW.IC-BOARD.DE

WEBSHOP IN-CIRCUIT GMBH

#### **FEATURES**

- Freescale i.MX536 Cortex-A8 Prozessor mit bis zu 800 MHz (1GHz in iMX535 Version)

- 512 MByte DDR3-RAM

- 8 MByte paralleler NOR-Flash für schnelles Booten

- 4 GByte NAND Flash

- integrierter 10/100 MBit Ethernet PHY

- Schnittstellen: Ethernet, USB Host+Device, SATA, UARTs, SPIs, CAN, ISO7816, LCD (TTL and LVDS), Camera IF...

- die meisten Pins sind auch als GPIO verwendbar

- Alle Spannungsregler integriert, Eingangsspannung 5V + -10%, Leistungsaufnahme typ. 1,5-2W

- SODIMM-200 Formfaktor (2.5V-Version-Sockel)

- Temperaturbereich -20°C bis +70°C

- zugelassen für Industrie und Wohnbereich

- passendes Entwicklungsboard ADB4001

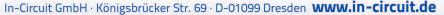

# Ethernet-Schnittstelle für das STM32F4 Discovery Board

Simon Tewes, Christoph Budelmann <mail@budelmann-elektronik.com>

#### Einleitung \_

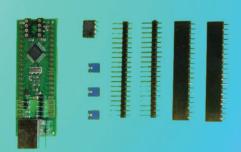

Die Firma ST Microelectronics bietet mit dem STM32F4 Discovery Board [1] ein sehr günstiges Entwicklungsboard mit interessanter Peripherie und einem sehr leistungsfähigen Mikrocontroller an. Das Board ist ideal für erste Schritte mit einem ARM Cortex-M4 basierten Mikrocontroller. In diesem Artikel soll das Board kurz vorgestellt sowie die Erweiterung des Boards um eine Ethernet-Schnittstelle

beschrieben werden, die auf dem Basisboard nicht vorhanden ist. Zum Test der Hardware dient dabei ein angepasstes Demo-Projekt von ST Microelectronics, über das die Leuchtdioden des Basisboards über eine Web-Oberfläche gesteuert werden können.

Abb. 1: STM32F4 Discovery Board

#### Hardware \_

Kern des STM32F4 Discovery Boards ist der STM32F407VG Mikrocontroller im LQFP100-Gehäuse, der mit einer maximalen Taktfrequenz von 168MHz arbeitet und dessen Pins vollständig auf zwei zweireihige Stiftleisten herausgeführt sind. Damit lässt sich das Board einfach und schnell um eigene Peripherie erwei-

tern. Ein Programmieradapter ist direkt auf dem Board integriert, so dass keine weiteren Adapter nötig sind um mit der Programmierung zu starten. Der sogenannte ST-LINK/V2 nutzt die SWD-Schnittstelle (Serial Wire Debug) des Mikrocontrollers. Die Verbindung mit dem PC erfolgt über eine Mini-USB-B-Buchse, die das Board auch mit Strom versorgen kann. Daneben sind auf dem Board ein dreiachsiger MEMS-Beschleunigungssensor, ein MEMS-Mikrofon, ein Audio-DAC mit Class-D Verstärker, acht Leuchtdioden, zwei Taster und ein Mikro-USB OTG Anschluss vorhanden.

#### Entwicklungsumgebung

Eine sehr interessante Hardware-Plattform nützt natürlich nichts, wenn keine passende Entwicklungsumgebung verfügbar ist. Im Folgenden möchten wir hier exemplarisch auf die Open-Source Entwicklungsumgebung CooCox [2] eingehen, die sich insbesondere für Einsteiger in die Welt der ARM-Programmierung sehr gut eignet.

CooCox CoIDE ist eine Entwicklungsumgebung, die auf Eclipse [3] basiert und viele Voreinstellungen bei der Installation bereits automatisch vornimmt. Ab der Version V1.4.1 unterstützt CoIDE die neuen ARM Cortex-M4 Mikrocontroller und bereits seit längerem den ST-LINK/V2. Außer der Toolchain für die ARM-Mikrocontroller wird keine weitere Software benötigt. Als Toolchain soll die GNU Toolchain for ARM Embedded Processors [4] verwendet werden, deren aktuelle Version die 4.6\_2012q2 ist.

Als Erstes sollte die GNU-Toolchain installiert werden und dann die CooCoxTools. CooCox bietet hierfür das CoCenter an, über das die CoIDE und CoFlash installiert werden können. CoFlash dient zum Übertragen der erzeugten BinärDatei auf den Mikrocontroller.

Ist die Installation abgeschlossen müssen noch einige wenige Einstellungen gemacht werden und es kann losgehen.

Zunächst startet man CoIDE und wählt in der Menüleiste

/Project/ Select Toolchain Path

Dort wird der Pfad zum "bin" Ordner der GNU-Toolchain eingetragen. Anschließend muss nur noch der Debugger eingestellt werden, nachdem ein Projekt angelegt wurde.

Dafür wählt man

/Project/New Project

in der Menüleiste aus, gibt dem Projekt einen Namen und wählt den Speicherort.

Auf der Startseite befindet sich nun der Reiter "Repository", sollte dieser sich dort nicht befinden, kann man diesen unter "View" aufrufen. Im nun folgenden Dialog werden die Rahmenbedingungen des neuen Projektes festgelegt. Für das STM32F4 Discovery Board wählt man

>>ST>>STM32F407VG

als Mikrocontroller aus. Auf den nun folgenden Seiten können Bibliotheken gewählt werden, die für das Projekt verwendet werden. Bei diesen Komponenten handelt es sich um die Standard-Bibliotheken von ST Microelectronics.

Als letzter Schritt folgt die Einstellung des Debuggers, um das Übertragen der Binärdatei auf das Board zu ermöglichen. Man öffnet in CoIDE den Reiter "Debug" in der Menüleiste und wählt "Debug Configuration". Unter "Cortex-M Application" befindet sich ein Punkt "XXX. configuration" der den vergebenen Projektnamen trägt. Dort trägt man unter Adapter den ST-Link/V2 ein und wählt als Port SWD. Nun kann das erste Programm geschrieben oder ein Beispielprojekt geöffnet werden.

ST Microelectronics liefert sehr umfangreiche Bibliotheken und Beispiele, diese können auf der ST Microelectronics Homepage unter "Design Support" für das STM32F4 Discovery Board heruntergeladen werden. In den Bibliotheken beziehungsweise Beispielen finden sich Beispiele für fast alle Peripheriekompo-

nenten des Discovery Boards und erleichtern somit einen Einstieg ungemein, zumal sie einem viel Recherche im doch sehr umfangreichen Datenblatt zum STM32F4 ersparen können.

#### Ethernet\_

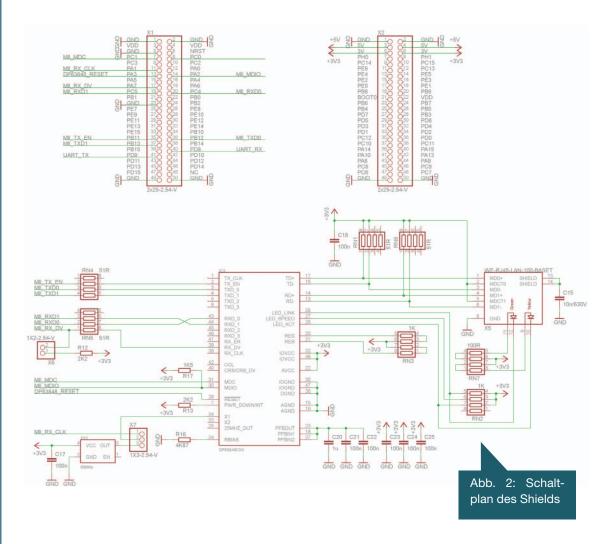

Um das Discovery Board Ethernet fähig zu machen bedarf es einiger zusätzlicher Hardware, welche in Form eines Aufsteckboards beziehungsweise "Shields" realisiert wurde. Da der STM32F407VG bereits einen Media Access Controller (MAC) integriert hat, beschränkt sich die zusätzliche Hardware auf die physikalische Schnittstelle, dem Phy und einer

RJ45-Buchse mit Übertrager. Als Ethernet-Phy wurde der DP8348 gewählt, zudem befindet sich auf dem Shield noch eine RJ45-Buchse mit integriertem Übertrager und zwei Leuchtdioden. Die Spannungsversorgung erfolgt über das Discovery Board. Grundsätzlich gibt es bei der Ansteuerung des Phy zwei Möglichkeiten, einmal per MII (Media Independent

Interface) und per RMII (Reduced Media Independent Interface). MII nutzt insgesamt acht Leitungen mehr als RMII, allerdings wird es auch nur mit der halben Taktrate von RMII betrieben. Da einige für MII benötigte Pins jedoch von den Peripheriebauteilen des Discovery Boards bereits belegt sind, wurde der Ethernet-Phy über RMII angebunden.

#### **Schaltplan**

Abbildung 2 zeigt den Schaltplan des Shields. Die Außenbeschaltung des Ethernet-Phy besteht dabei lediglich aus einer Hand voll passiver Bauteile und dem Quarzoszillator zur Erzeugung eines 50MHz Taktes.

Anzeige

### Bücher, Bausätze und Komplettsets

BS1013 - Bausatz Android Interface Board (IOIO-Clone) 37,00 €\*

06103 - Bausatz USB-Modul PML2232 mit dem FT2232D 28,00 €\*

BS1016 - Bausatz DC-Motor Treibermodul mit dem L298 12,00 €\*

BS1015 - Bausatz DC-Motor Treibermodul mit dem L293 8.00 €\*

BS1009 - Bausatz Universal Lauflicht mit Attiny861 8,00 €\*

\*Alle Preise inkl. MwSt zzgl. Versand

Anbieter: IB B. Redemann Mahlower Str. 204 14513 Teltow (kein Ladengeschäft!)

Hier im Shop: www.b-redemann.de

#### **Software**

ST Microelectronics bietet auf seiner Homepage ein Ethernet-Beispiel namens "Webpage Demonstration" an, das für das STM3240G-Eval-Board geschrieben wurde und sich sehr einfach an das Discovery Board anpassen lässt. Ein Projektordner inklusiver aller Anpassungen für das Discovery Board und die CoIDE An-

passung können dem Blog von TKJ Electronics [5] entnommen werden.

Das Projekt umfasst einen kleinen Webserver, der eine Website ins Netzwerk stellt und über diese einige Funktionen des Boards zugänglich macht. Es ist dabei sowohl möglich, die IP-Adresse des

Boards fest einzustellen als auch DHCP zu nutzen. Die Einstellung hierzu findet sich in der main.h. Über die Eingabe der IP-Adresse im Browser wird die Website aufgerufen und es können über diese die Leuchtdioden ein- und ausgeschaltet sowie ein AD-Wandler-Kanal ausgelesen werden.

#### **Zusammenfassung**

Sowohl für Neueinsteiger in die Welt von Mikrocontrollern als auch für Umsteiger, die die Leistungsfähigkeit von 32bit Mikrocontrollern erforschen wollen, eignet sich das Discovery Board in idealer Weise. Erfahrungen im Einrichten einer ARM-Toolchain und IDE sind bei der Verwendung der CooCox Umgebung ebenfalls nicht nötig, womit schnelle erste Erfolge garantiert sein sollten. Mit der nachgerüsteten Ethernet-Schnittstelle eignet sich das Discovery Board aber auch für anspruchsvollere Mess-, Steuerund Regel-Anwendungen im Netzwerk oder auch als einfacher Webserver.

#### Literatur\_

[1] STM32F4 Discovery Board: http://www.st.com/internet/eval-board/product/252419.jsp

[2] CooCox Entwicklungsumgebung: http://www.coocox.org

[3] Eclipse: http://www.eclipse.org

[4] GCC Toolchain for ARM Embedded: https://launchpad.net/gcc-arm-embedded

[5] Angepasstes "Website Demonstration" Projekt für CooCox: http://blog.tkjelectronics.dk/2012/08/ethernet-on-stm32f4discovery-using-external-phy/

### **USB-CAN Adapter**

#### **Praktikumsbericht**

Seit September bin ich Praktikantin bei Lessmüller Lasertechnik in München und absolviere dort mein Praxissemester. Lessmüller Lasertechnik stellt Prozessüberwachungssysteme für das Laserstrahlschweißen her. Um in zukünftigen Projekten die Evaluierung von CAN-Bus-Sensoren via USB vornehmen zu können, wurde mir die Aufgabe zugeteilt eine Hard- und Software zu entwickeln, die dies einfach und zugleich flexibel ermöglicht.

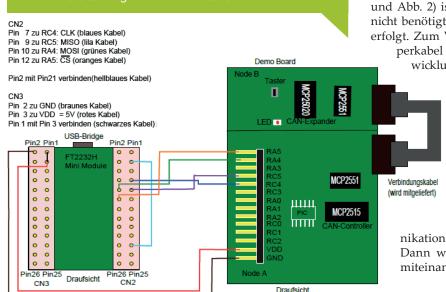

#### **Die Hardware**

Um nicht viel Zeit mit dem Layouten von Platinen zu verbringen, wird die Hardware aus zwei fertigen Entwicklungsboards zusammengesteckt.

Das zentrale Herzstück

des USB-CAN Adapters bildet der CANController MCP2515

von Microchip. Hierbei

handelt es sich um einen CAN-Controller, der

über eine SPI Schnittstelle angesprochen wird und

CAN Nachrichten senden und

empfangen kann. Er wird mit 5V versorgt.

Zudem wird ein CAN-Transceiver wie der MCP2

Zudem wird ein CAN-Transceiver wie der MCP2551 zwischen der Busleitung und dem CAN-Controller verwendet.

Beide ICs finden sich auf dem MCP2515 PictailTM Demo Board von Microchip [1]. Außerdem enthält das Board eine abtrennbare Platine mit dem CAN-Expander MCP25020, einer LED und einem Taster. Der MCP25020 ist bereits vorprogrammiert und kann zum Testen der CAN Kommunikation eingesetzt werden. Zum Einschalten der LED muss eine CAN Message an den CAN-Expander mit ID, Länge, Adresse, Maske und Da-

EZOROBA NICHOCHIP NODE B NODE B TEEN BE STORED TO THE STOR

Abb. 1: Testaufbau

ten gesendet werden. Der Zustand des Tasters kann durch eine Request Message\*, die

aus ID und Datenlänge besteht, ermittelt werden.

Da die meisten PCs nicht über eine SPI Schnittstelle verfügen wird das FT2232H Mini Module von FTDI [2] als USB Bridge eingesetzt. Dies ist ebenfalls als Entwicklungsboard mit allen benötigten Bauteilen wie z.B. Spannungsregler, Oszillator, etc. erhältlich. Die USB Bridge kann je nach verwendeter SW-Bibliothek als UART, JTAG, I²C und SPI Bridge verwendet werden. Zudem verfügt sie über mehrere Kanäle.

Die Verdrahtung der beiden Entwicklungsboards (siehe Abb. 1 und Abb. 2) ist relativ einfach. Ein zusätzliches Netzteil wird nicht benötigt, da die Versorgung über den USB-Port des PCs erfolgt. Zum Verbinden der einzelnen Steckpins werden Jum-

perkabel eingesetzt. Zunächst muss auf dem FTDI Entwicklungsboard Pin1 (CN3) mit Pin 3 (CN3) verbun-

den werden, damit der 3,3V Spannungsregler mit der 5V Stromversorgung des USB Busses versorgt wird. Weiterhin ist es notwendig Pin3 (CN2) mit Pin21 (CN2) zu verbinden. Diese Verbindung sorgt für die richtige Betriebsspannung von 3,3V für VCCIO auf dem FT2232H Chip.

Anschließend wird auf dem MCP2515 PictailTM Demo Board der Microcontroller PIC16F676 herausgelötet, damit er die Kommu-

nikation zwischen MCP2515 und FT2232H nicht stört. Dann werden die SPI-Pins MISO, MOSI, CLK und CS miteinander verbunden. Eine Kreuzung der Datenpins

#### Abb. 2: Verdrahtung der beiden Boards

13

wie beispielsweise bei UART, ist bei SPI nicht nötig. Zur Versorgung des CAN-Controllers und des CAN-Transceivers muss eine weitere Leitung mit 5V (Pin3 CN3 zu VDD) verbunden werden. Natürlich braucht es abschließend noch eine GND Verbindung.

#### Die Software

Die Software besteht aus einem einfachen Konsolenprogramm, das sich aus drei Ebenen zusammensetzt.

- SPI Ebene: Von FTDI gibt es eine fertige Bibliothek [3] anhand derer die SPI Funktionen des Mini Modules mit wenigen Befehlen (read, write, open, close, get channels, init channels ...)genutzt werden können

- MCP2515 Ebene: Des Weiteren enthält das Konsolenprogramm die MCP2515 Bibliothek von Fabian Greif [4]. Hier sind allerdings einige Anpassungen notwendig, da die Bibliothek ursprünglich für Mikrocontroller und nicht für PC basierte Anwendungen geschrieben wurde. In der Bibliothek findet man Funktionen mit denen man Register auslesen und beschreiben kann, aber auch den Mikrocontroller initialisieren und in verschiedene Zustände (listen, sleep ...) setzen kann.

- CAN Ebene: Zur komfortablen Nutzung des CAN Adapters in eigenen Programmen gibt es die folgenden Funktionen: CAN: init, set ID, send data, get message, set mode, close. Sie greifen allesamt auf Funktionen der MCP2515 und FT2232 Bibliotheken zu.

- Im Beispielprogramm (siehe rechts) wird im Anschluss an eine grundsätzliche Initialisierung das Konsolenprogramm fortlaufend in einer While-Schleife ausgeführt. Es wird geprüft, ob die Taste auf dem Expander Board gedrückt wurde und sendet ggf. eine CAN Message zum Ein- oder Ausschalten der LED.

Der TXB0 Sendepuffer wird dauerhaft mit der ID 0x500 beschrieben. Somit ist es ausreichend zum Schalten der LED lediglich die data[] Bytes zu manipulieren und das gesamte Paket aus dem Sendepuffer TXB0 zu verschicken. Erhält der Expander eine CAN Message mit der ID 0x500 und data[2] = 0x00, so wird die LED eingeschaltet. Ist data[2] = 0x10, dann schaltet die LED wieder ab.

```

#include <conio.h>

#include <stdio.h>

#include <stdlib.h>

#include "can.h"

void main(void)

can t msg;

uint8 data[8];

data[0] = 0x1E;

// Adresse des zu beschreibenden

Register

data[1] = 0x10;

// Maske

if (can init(BITRATE 125 KBPS))

// Empfangspuffer leeren

can _ get _ message(&msg);

/\!/ CAN ID 0x500 in Sendepuffer TXB0 schreiben

can _{\rm set} _{\rm id}(0x500, 0, TXB _{\rm 0}); // ID 0x500, keine

// extended ID, Puffer TXB0

/\!/ CAN ID 0x280 in Sendepuffer TXB1 schreiben

can set id(0x280, 0, TXB 1); // ID 0x280, keine

// extended ID, Puffer TXB1

do

{

// Nachricht aus Sendepuffer TXB1 versenden

can send data(0, 8, Rtr, TXB 1); // keine

// Daten, Länge 8, RTR Nachricht, Puffer TXB1

// Empfangene Nachrichten abfragen

can get message(&msg);

// empfangene Daten auswerten

if((msg.data[1] \& 0x01) == 0x00)

// wenn Taste gedrueckt, LED an

{

data[2] = 0x00;

printf("Taste gedrueckt, LED an\n");

else

// sonst LED aus

{

data[2] = 0x10;

printf("Taste nicht gedrueckt, LED

aus\n");

// Nachricht senden, ob LED an oder aus

can send data(data, 3, 0, TXB 0); // Daten,

//Länge 3, keine RTR Nachricht, Puffer TXB0

} while(! kbhit()); // zyklisch fortlaufend bis

//belibige Tastatureingabe kommt

can _ close();

}

}

```

Wenn der Expander eine CAN Message mit der ID 0x280 und einem gesetzten RTR Flag empfängt, wird er mit der geforderten Datenanzahl antworten. Im Bespielprogramm mit 8 Byte, das entspricht Daten aus 8 Registern. Um den Tastendruck abzufragen, wird in diesem Fall das 2. Register ausgelesen, wenn in diesem 0x01 drinsteht wurde die Taste nicht gedrückt bei 0x00 wurde sie gedrückt.

#### **Fazit**

Das beschriebene Projekt stellt eine schnelle und sehr flexible Möglichkeit dar einen USB-CAN Adapter selber zu bauen. Der Aufbau der Hardware ist auf Grund der verwendeten Entwicklungsboards sehr gering. Die Software ermöglicht einen unbegrenzten Zugriff auf alle Funktionen des CAN-Controllers. Somit ist es mit etwas programmieren möglich weitere Projekte wie z.B. einen USB-CAN-Logger aufzubauen. Das Praktikum bei Lessmüller Lasertechnik war eine interessante Herausforderung für mich. Ich konnte mich in den Bereichen Elektronik und Programmieren weiterbilden. Dies geschah nicht nur durch das Projekt, sondern auch durch interessante Gespräche mit den anderen Studenten und Mitarbeitern. Zudem hat es Spaß gemacht an einem abgeschlossenen Projekt zu arbeiten, welches sich später in den Produkten wieder finden wird.

#### Links/ Download

- [1] http://ww1.microchip.com/downloads/en/DeviceDoc/51572a. pdf

- [2] http://www.ftdichip.com/Support/Documents/DataSheets/Modules/DS\_FT2232H\_Mini\_Module.pdf

- [3] http://www.ftdichip.com/Products/ICs/FT2232H.htm (Datenblatt, Driver, DLL)

- [4] http://www.kreatives-chaos.com/artikel/universelle-canbibliothek

- [5] USB-CAN-Adapter.zip im Forum (siehe Einleitung S. 2 im Journal)

rtiizeige

Haben Sie auch Interesse bei Lessmüller Lasertechnik Ihr Praktikum oder Ihre Ausbildung zu absolvieren? Wir bieten fortlaufend Stellen für

#### Praktikanten / Auszubildende (Fachinformatiker) / Studenten (m/w)

In unserer Firma erwartet Sie ein interessanter und abwechslungsreicher Arbeitsplatz mitten in München. Wir sind ein ambitioniertes Team aus Naturwissenschaftlern, Ingenieuren, Informatikern, Quereinsteigern, Auszubildenden und Studenten. Eine flache Hierarchie mit kurzen Entscheidungswegen bietet Freiraum für Ihre persönliche Entwicklung.

Wir freuen uns auf Ihre Bewerbung.

Lessmüller Lasertechnik GmbH Gollierstraße 12, D-80339 München Telefon: +49 (0)89 / 360 90 48 – 0 Telefax: +49 (0)89 / 360 90 48 – 29 Email: bewerbung@lessmueller.de Website: www.lessmueller.de

### Vom Überweisungsauftrag zur TAN

#### **Andreas Schiermeier**

In den letzten Jahren sind viele Banken und Sparkassen dazu übergegangen, iTAN-Listen auf Papier durch transaktionsgebundene mTAN (TAN per SMS auf das Handy) oder TAN-Generatoren abzulösen. Diese werden je nach Institut unter den Bezeichnungen Sm@ artTAN, chipTAN, oder auch "Flicker TAN" beworben. Stets wird dabei pro Auftrag eine "flackernde" Grafik zum Einlesen mit dem bereitgestellten TAN-Generator dargestellt. Dieser zeigt nach dem erfolgreichen Einlesen die Transaktionsdaten an und liefert nach deren Bestätigung durch den Benutzer eine TAN. Die Spezifikation der dahinter stehenden Vorgänge ist nicht allgemein einsehbar. Dieser Artikel beschreibt gemachte Beobachtungen dieses Verfahrens hinsichtlich der optischen Schnittstelle zwischen Flickergrafik und Lesegerät sowie die Smartcardkommunikation. Denkbar wäre, diese Technik (insbesondere die damit, zumindest deutschlandweit, gut verbreiteten Generatoren anderweitig zu nutzen. Über Ergänzungen, Anmerkungen oder Korrekturen freuen wir uns.

#### **Ausgangspunkt**

Es wird eine Überweisung von 1,23 EUR an die Kontonummer 335554 im Onlinebanking beauftragt. Es muss der angezeigte "Flickercode" mit dem TAN-Generator bei eingelegter Bankkarte und nach Betätigung der Taste F eingelesen und die im Display angezeigten Transaktionsparameter, Kontonummer und Betrag, bestätigt werden. Schlussendlich zeigt der TAN-Generator die TAN 251067 zur Eingabe im Onlinebanking. Es ist zu beobachten, dass bei wiederholter Einlese- & Bestätiungs- pro-

zedur unterschiedliche TANs erzeugt werden. Werden auf diese Weise zuviele TANs erzeugt, jedoch nicht im Online-Banking verwendet, fordert das Bankssystem eine Neusyncronisation mit der Karte an.

Frage: Wie kommt der TAN-Generator zur Anzeige der TAN 251067?

#### Onlinebanking Interface -

**Flickercode Anzeige:** Das Onlinebanking zeigt einen "Flickercode". Dies kann über unterschiedliche Techniken erfolgen:

- · Adobe Flash Film

- Javascript & DOM

- animiertes GIF

- Java-Applet

- innerhalb einer nativen Applikation (z.B. StarMoney)

Die Auswahl der Darstellungstechnik richtet sich den verfügbaren Browsererweiterungen und Clienttechnologien (z.B. Terminalserver). Wenn möglich wird dem Flash Film der Vorzug gegeben.

#### Verbrauchertipp:) -

Gelingt das Einlesen der Grafik mit dem TAN-Generator nicht oder nur sehr unzuverlässig kann es helfen die Anzeigehelligkeit am Monitor/Display und Flickergeschwindigkeit der Grafik zu variieren. Ist die Anzeigehelligkeit zu hoch erkennt der Generator selbst schwarze Bereiche als "hell"; ist sie zu niedrig können entsprechend helle Balken nicht mehr differenziert werden. Einzelne Anzeigetechniken des Flickercodes (z.B. das üblicherweise verwendete Flash) erlauben desweiteren die Flickergeschwindkeit anzupassen. Ein Klick auf den ganz linken der fünf "flackernden" Balken verlangsamt den Ablauf der Sequenz. Dem gegenüber beschleunigen Klicks auf den Balken ganz rechts. So kann ein Kompromiss zwischen schnellem Einlesen der Daten und der Toleranz gegenüber Anzeigeproblemen (Browser, Grafiksystem, Monitor. etc) gefunden werden.

#### Flickercode Aufbau

Der Flicker-Code wird aus folgenden Eingabedaten generiert (im Folgenden "Flickerdaten" genannt):

0F 04 87 11 00 03 03 33 55 54 14 31 2C 32 33 1D

Diese, bzw. eine entsprechende, Zahlenreihe findet sich auch im Quelltext der Onlinebanking-Seite als Parameter für den Flash Film oder die Javascript- & DOM-Routine.

Die Flickerdaten werden beispielsweise wie folgt zusammengestellt:

Abb. 1: Testaufbau

```

OF: Anzahl nachfolgender Bytes (15 Bytes)

0 : Kennzeichen der Kodierung für die nachfolgenden Daten in BCD (0=BCD, 1=ASCII)

4: Länge des sog. Start-Codes in Bytes (der Start-Code definiert die vom TAN-Generator ange-

zeigten Masken)

87 11 00 03: 4 byte Start-Code in BCD-Notation - S

: signalisiert freie Maskengestaltung anhand nachfolgender Codes (hier 7 und 1)

8

: signalisiert Maske "Kontonummer"

: signalisiert Maske "Betrag"

1 00 03: Übergabe einer vom Bankensystem vorgegebenen Zufallszahl (ändert mit jeder On-

line-Transaktion)

0 : Kodierung der nachfolgenden Daten in BCD

3: Länge des ersten Maskeninhalts in Byte

33 55 54: 3 Byte: erster Maskeninhalt (Kontonummer) in BCD-Notation - M1

1 : Kodierung der nachfolgenden Daten in ASCII (wg. Komma in 1,23)

4: Länge des zweiten Maskeninhalt in Bytes

Hinweis:

302C3031: zweiter Maskeninhalt (hier: Betrag) in ASCII-Kodierung 1,23 - M2

: ASCII (hex): 1

31

: ASCCI (hex): , (Komma)

32 : ASCII (hex): 2

33: ASCII (hex): 3

1 : Luhn Prüfsumme über Start-Code und Maskeninhalte

gefüllt.

D: XOR Prüfsumme über die gesamten Flickerdaten ohne diese beiden Prüfsum-

```

Eine ungerade Anzahl an BCD-Stellen (1/2 Byte) in Maskenwerten wird mit einem "F" als Füllzeichen zu einem vollen Byte auf-

#### Luhn-Prüfsumme -

menhalbbytes

Bildung der Luhn-Prüfsumme über Start-Code S und Maskeninhalte M1 & M2:; Vorgehen:

- 1) Jedes linke Halbbyte zählt einfach, jedes rechte Halbbyte zählt doppelt

- 2) Aus allen einzelnen Werten von 1. werden jeweils Quersummen gebildet und diese summiert

- 3) Die Prüfsumme ist 10-(Summe aus 2. modulo 10)

S-----|M1-----|M2-----Am Beispiel : 87 11 00 03 33 55 54 31 2C 32 33: : 8 +1 +0 +0 +3 +5 +5 +3 +2 +3 +3 1x1 Quersumme 1x1: 8 + 1 + 0 + 0 + 3 + 5 + 5 + 3 + 2 + 3 + 3 = 33: 14+ 2+ 0+ 6+ 6+10+ 8+ 2+24+ 4+ 6 Quersumme 2xr: 5+ 2+ 0+ 6+ 6+ 1+ 8+ 2+ 6+ 4+ 6=46 Summe: 79 10-(Summe modulo 10):

#### **XOR**

Bildung der XOR-Prüfsumme am Beispiel:

OF 04 87 11 00 03 03 33 55 54 14 31 2C 32 33

Die Operation erfolgt in Übertragungsreihenfolge (erst niederwertiges Halbbyte, dann höherwertiges, 0F->F0, 0440, ...)

F0 40 78 11 00 30 30 33 55 45 41 13 C2 23 33

#### Berechnung

0x0 ^ 0x4 ^ 0x0 ^ 0x7 ^ 0x8 ^ 0x1 ^ 0x1 ^ 0x0 ^ 0x0 ^ 0x3 ^ 0x0 ^ 0x3 ^ 0x0 ^ 0x3 ^ 0x3 ^ 0x5 ^ 0x5 ^ 0x4 ^ 0x5 ^ 0x4 ^ 0x1 ^ 0x1 ^ 0x3 ^ 0xC ^ 0x2 ^ 0x2 ^ 0x3 ^ 0x3 ^ 0x3 = 0xD

#### Flickercode Übertragung

Die optischen Eingänge des TAN-Generators nehmen ein Taktsignal und je ein Halbbyte (4 bit, auch genannt Nibble) an Daten entgegen. Die Abfolge der Signalfelder ist wie folgt (auf dem Bildschirm).

| Feld 1 | Feld 2 | Feld 3 | Feld 4 | Feld 5 |

|--------|--------|--------|--------|--------|

| Takt   | 2^0    | 2^1    | 2^2    | 2^3    |

Der eigentlichen Übertragung wird eine statische Synchronisationssequenz vorgelagert:

Flicker zum "Mitschreiben":

- 1) Flicker-GIF von Onlinebanking-Service erzeugen lassen

- wget –no-check-certificate

Oflicker.gif "https://Home-bankingserver/InternetPortal-Struts/CreateFlickerImage?dat

a=...&fps=10"

| Fel | d 1 | Feld 2 | Feld 3 | Feld 4 | Feld 5 |

|-----|-----|--------|--------|--------|--------|

| 1   |     | 0      | 0      | 0      | 0      |

| 0   |     | 0      | 0      | 0      | 0      |

| 1   |     | 1      | 1      | 1      | 1      |

| 0   |     | 1      | 1      | 1      | 1      |

| 1   |     | 1      | 1      | 1      | 1      |

| 0   |     | 1      | 1      | 1      | 1      |

| 1   |     | 1      | 1      | 1      | 1      |

- $\hbox{--} z.B.\ wget\ -- no-check-certificate\ -- Oflicker.gif\ "https://bankingportal.frankfurter-sparkasse.de/InternetPortalStruts/Creat"}$

- 2) herunterladen e Flicker<br/>Image?data=0 F04871100030333555414312C32331D &fps=10"

- 3) mit "gimp" öffnen und Layer-Ansicht anzeigen Abbildung 2

#### TAN-Generator\_\_\_\_

Zur TAN-Erzeugung wird die Bankkarte in den TAN-Generator gesteckt und mit der Funktionstaste "F" das Einlesen gestartet. Der Flickercode wird über die Fototransistoren auf der Rückseite eingelesen.

Die Tests erfolgten größtenteils mit einem REINER SCT tanJack® optic SR.

Die Schritte im Einzelnen:

# Funfact/Eselsbrücke: Betrachtet man nur die Felder 2-5 bei wechselndem Takt: 0x0 0xf 0xf -> hex-speak: "Off", gefolgt von Takt=0b1, Rest=0xf.

Im Anschluss werden die Flickerdaten, jeweils beginnend mit dem niederwertigsten Halbbyte, übertragen. Mit der steigenden Flanke des Takts beginnt ein neues Halbbyte.

Am Beispiel von 0F0487...:

| Wert | Takt | 2^0 (1) | 2^1 (2) | 2^2 (4) | 2^3(8) |

|------|------|---------|---------|---------|--------|

| F    | 1    | 1       | 1       | 1       | 1      |

| 0    | 0    | 1       | 1       | 1       | 1      |

|      | 1    | 0       | 0       | 0       | 0      |

|      | 0    | 0       | 0       | 0       | 0      |

| 4    | 1    | 0       | 0       | 1       | 0      |

|      | 0    | 0       | 0       | 1       | 0      |

| 0    | 1    | 1       | 0       | 0       | 0      |

|      | 0    | 1       | 0       | 0       | 0      |

| 7    | 1    | 1       | 1       | 1       | 0      |

|      | 0    | 1       | 1       | 1       | 0      |

| 8    | 1    | 0       | 0       | 0       | 1      |

|      | 0    | 0       | 0       | 0       | 1      |

#### a. Initialisierung

Nach dem Einstecken der Bankkarte ist mit einem Logic Analyzer Saleae Logic folgendes an Kontakten der Smartcard zu beobachten:

- Spannungsversorgung via VCC startet

- I/O wird auf HIGH gesetzt

- das CLK-Signal startet

- RST wird auf HIGH gesetzt

Die Kommunikation im Weiteren auf der I/O-Leitung zwischen Terminal und Karte wurde mittels Bus Pirate v2go mitgeschnitten.

Abb. 2: Kontakte [2]

#### Testaufbau:

Die Signalleitungen VCC, RST, CLK, GND, I/O müssen zwischen Terminalinterface (im Bild

| Signalleitung | Bus Pirate Pin |

|---------------|----------------|

| GND           | GND            |

| CLK           | AUX            |

| 1/0           | MISO           |

unter Zuhilfenahme eines passenden dünnen Platine) und der Chipkarte 1:1 verbunden werden. Die Signalleitungen GND, CLK und I/O werden des weiteren dem Bus Pirate zugeführt:

Folgende Firmwareversion des Bus Pirate kam zum Einsatz:

```

HiZ>i

Bus Pirate v3.a

Firmware v6.1 r1676 Bootloader v4.1

DEVID:0x0447 REVID:0x3042 (24FJ64GA002 B4)

http://dangerousprototypes.com

HiZ>

```

#### Parametrisierung des Bus Pirate [3]:

Um die Kommunikation mitschneiden zu können muss Anfangs muss die vom TAN-Generator der Karte vorgegebene Taktfrequenz ermittelt werden. Zu diesem Zweck bietet der Bus Pirate eine Frequenzmessung auf dem AUX PIN an; welche mit dem Befehl "f" aufgerufen wird. Es ist empfehlenswert, diesen Vorgang mehrmals zu wiederholen. Die Messung ist nur nach dem Einführen der Karte in den Generator und während der Kommunikation mit der Karte möglich. Der Bus Pirate benötigt ein über eine Sekunde dauerhaft anliegendes Takt-Signal.

```

HiZ>fffffff

AUX Frequency: autorange 0 Hz

AUX Frequency: autorange 392,394 Hz

AUX Frequency: 450,304 Hz

AUX Frequency: 1,644,800 Hz

AUX Frequency: autorange 392,394 Hz

AUX Frequency: autorange 0 Hz

HiZ>

```

Mit Hilfe der Taktrate kann der Wert des BRG errechnet werden (vgl. Berechnung BRG):

```

(4000000/1644800*372)-1 = 903,66926 => 904

```

Damit kann nun der UART-Modus des Bus Pirate parametrisiert werden:

```

HiZ>m3

Set serial port speed: (bps)

1. 300

2. 1200

3. 2400

4. 4800

5. 9600

6. 19200

7. 38400

8. 57600

9. 115200

10. BRG raw value

```

```

Raw value for BRG (MIDI=127)

(34) > 904

Data bits and parity:

1. 8, NONE *default

2. 8, EVEN

3. 8, ODD

4. 9, NONE

(1)>2

Stop bits:

1. 1 *default

2. 2

(1)>2

Receive polarity:

1. Idle 1 *default

2. Idle 0

(1)>

Select output type:

1. Open drain (H=Hi-Z, L=GND)

2. Normal (H=3.3V, L=GND)

(1)>

Ready

Mit "{" wird die Ausgabe gestartet:

UART>{

UART LIVE DISPLAY, } TO STOP

UART>

READ: -f 0x00

UART>

Damit gibt der Bus Pirate die einzelnen

Bytes in folgendem Format aus:

IJART>

READ: 0x3B

UART>

READ: 0xFF

UART>

READ: 0x18

UART>

READ: 0x00

UART> ...

```

In den nachfolgenden Schritten werden die Byte mit Leerzeichen getrennt und, der Übersicht zuliebe, ohne 0x-Präfix dargestellt. Mit "T->C" ist im Folgenden die Kommunikation vom TAN-Generator/Terminal zur Karte markiert, von der Karte zum Terminal mit "T<-C".

#### b. ATR

Nach dem Anlegen der RST-Signals liefert die Karte den ATR (Answer to Reset) aus und der TAN-Generator überprüft, ob die ZKA TAN-Generatoranwendung angewählt werden kann. Im Anschluss beendet der Generator wieder die Kommunikation mit der Karte (alle Kontakte LOW) bis der Benutzer die Taste "TAN" oder "F" betätigt. Es startet die Initialisierungssequenz wie oben und der ATR wird erneut gesendet. In den Beispielen ist der Seriennummer des Chips im ATR mit "SS SS SS SS" überschrieben.

#### T-> C 3B FF 18 00 FF 81 31 FE 45 65 63 11 08 43 02 50 00 10 SS SS SS SS 05 30 6C

Der ATR kann mit dem Script ATR\_analysis aus den http://ludovic.rousseau.free.fr/softwares/pcsc-tools/ bequem aufbereitet werden:

```

(pcsc-tools-1.4.18)$ ./ATR analysis 3B FF 18 00 FF 81 31 FE 45 65 63 11 08 43 02 50 00 10 SS SS

SS SS 05 30 6C

ATR: 3B FF 18 00 FF 81 31 FE 45 65 63 11 08 43 02 50 00 10 SS SS SS SS 05 30 6C

+ TS = 3B --> Direct Convention

+ T0 = FF, Y(1): 1111, K: 15 (historical bytes)

TA(1) = 18 --> Fi=372, Di=12, 31 cycles/ETU

129032 bits/s at 4 MHz, fMax for Fi = 5 MHz => 161290 bits/s

TB(1) = 00 \longrightarrow VPP is not electrically connected

TC(1) = FF --> Extra guard time: 255 (special value)

TD(1) = 81 \longrightarrow Y(i+1) = 1000, Protocol T = 1

TD(2) = 31 --> Y(i+1) = 0011, Protocol T = 1

TA(3) = FE \longrightarrow IFSC: 254

TB(3) = 45 --> Block Waiting Integer: 4 - Character Waiting Integer: 5

+ Historical bytes: 65 63 11 08 43 02 50 00 10 SS SS SS SS 05 30

Category indicator byte: 65 (proprietary format)

TCK = 6C (correct checksum)

```

Demnach hat der Datenaustausch mit der Karte nach dem T=1 Protokoll zu erfolgen (auch ersichtlich an TCK. TCK wird nur bei T=1 gesendet).

T=0 vs. T=1:

- T=0: Byteorientiertes Protokoll. Jedem übertragenem Byte wird ein Parity-Bit angehängt. Ist die Parity nicht korrekt zieht der Empfänger die Leitung I/O auf HIGH und der Sender wiederholt anschließend das Byte.

- T=1: Blockorientiertes Protokoll. Die Kommandos und Antworten werden mit einem Header eingeleitet, am Stück übertragen und eine XOR-Prüfsumme angehängt. Bei einem Übertragungsfehler wird vom Empfänger der Block erneut angefordert (mit einer Steuernachricht).

Aufbau der Nachrichten:

#### I Block (normale Datenübertragung)

| _ | 1   | Derko | NIAD | (NIada | A d dwage | Dr.ta) |

|---|-----|-------|------|--------|-----------|--------|

| • | - 1 | byte  | NAD  | uvoae  | Address   | byte   |

1 Byte PCB (Protocol Control Byte)

I Information Block

R Receive Ready Block

S Supervisory Block

| b8 | b7                 | b6                             | b5      | b4 b3     | b2      | b1      |

|----|--------------------|--------------------------------|---------|-----------|---------|---------|

| 0  | Sende Sequenz (ab- | 1: weiterer verketteter Daten- | 0 (RFU) | 0 (RFU) 0 | 0 (RFU) | 0 (RFU) |

|    | wechselnd 0 und 1) | block folgt, sonst 0           |         | (RFU)     |         |         |

|    |                    |                                |         |           |         |         |

• 1 Byte Länge 0..254 (FE)

#### R Block (Status)

| • | 0  | 254  | Byte       | Daten |

|---|----|------|------------|-------|

| - | v. | .201 | $D_{V}$ ic | Daten |

- 1 Byte XOR Prüfsumme ab und inkl. NAD

- NAD ist immer 0x00 (vorgesehen für zukünftige Verwendung)

- PCB siehe Tabellen unten

|   | b8 | b7 | b6      | b5                        | b4 b3   | b2         | b1                           |

|---|----|----|---------|---------------------------|---------|------------|------------------------------|

| ĺ | 1  | 0  | 0 (RFU) | Empfangs Sequenz (abwech- | 0 (RFU) | 0          | 0: kein Fehler               |

|   |    |    |         | selnd 0 und 1)            | 0 (RFU) |            |                              |

|   |    |    |         |                           |         | 0          | 1: Checksummen- oder Parity- |

|   |    |    |         |                           |         |            | fehler                       |

|   |    |    |         |                           |         | 1: anderer | 0                            |

|   |    |    |         |                           |         | Fehler     |                              |

S Block (Protokollsteuerung)

|    |    |                         |    |       | o block (Frotokonoteacrang)     |           |  |  |

|----|----|-------------------------|----|-------|---------------------------------|-----------|--|--|

| b8 | b7 | b6                      | b5 | b4 b3 | b2                              | b1        |  |  |

| 1  | 1  | 0: Request, 1: Response | 0  | 0 0   | 0                               | 1: Resync |  |  |

|    |    |                         |    |       | 1: Information Field Size (IFS) | 0         |  |  |

IFS gibt die Puffergröße an, es wird hierbei zwischen Terminal und Karte unterschieden

• IFSD: Empfangspuffer des Terminals; Startwert 32 Byte

IFSC: Empfangspuffer der Karte wird im ATR mitgeteilt (siehe oben: 0xFE, 254)

Quelle, abseits eingeschränkt verfügbarer ISO-Standards: http://www.panstruga.de/ct-api/spec/mktp2v09.ps.gz

#### Historical Bytes

Die "Historical Bytes" (im Beispiel "65 63 11 08 43 02 50 00 10 SS SS SS SS 05 30", siehe oben) des ATR haben bei SECCOS Karten folgende Bedeutung (Quelle)

| Feld (1 Byte)                         | Wert |

|---------------------------------------|------|

| fix                                   | 65   |

| fix                                   | 63   |

| IC manufacturer ID                    | 1 1  |

| Manufacturer's IC type ID             | 08   |

| Manufacturer's ROM mask ID            | 43   |

| Embedder country code                 | 02   |

| Embedder country code                 | 50   |

| Embedder national registration ID     | 00   |

| Embedder national registration ID     | 10   |

| Chip series number                    | SS   |

| Manufacturer OS Version (major versi- | 05   |

| on number)                            |      |

| Manufacturer OS Version (minor versi- | 30   |

| on number)                            |      |

Die SECCOS-Version, hier "05.30", ist von besonderer Bedeutung, da ab Version 6.0 der Ablauf geringfügig abweicht.

#### c. T=1 IFSD

Nachdem die Karte dem Terminal im ATR mitgeteilt hat, dass die Datenübertragung via T=1 erfolgt, wird ein S-Block Request geschickt um den IFSD zu erhöhen.

Das Terminal (T) teilt der Karte (C) per S-Block Request (110. ....) die Größe (FE = 254 byte) des Empfangspuffers IFSD (.... ...1) mit:

T->C 00 C1 01 FE 3E

Die Karte bestätigt dies per S-Block Response (111. ....).

T<-C 00 E1 01 FE 1E

Ab diesem Zeitpunkt folgen nur noch I Blöcke zwischen Terminal und Karte - die eigentliche Kommunikation. Innerhalb einer PCSC-Applikation können diese nachfolgenden APDUs direkt verwendet werden (ohne die vorderen drei T=1-Header- und das abschließende Prüfsummen-Byte)

#### d. SELECT FILE

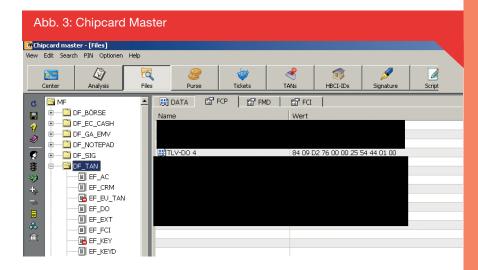

Im ersten Schritt wird mittels SELECT FILE die Datenstruktur des TAN-Generator ausgewählt. AID ermittelt in Chipcard Master:

| <->  | T=1 Header | APDU                                      | T = 1 |

|------|------------|-------------------------------------------|-------|

|      |            |                                           | XOR   |

| T->C | 00 00 0E   | 00 A4 04 0C 09 D2 76 00 00 25 54 44 01 00 | 3B    |

| T<-C | 00 00 02   | 90 00                                     | 92    |

AID

Aufbau des AID (Application Identifier) aus RID (Registered Application Identifier) und PIX (Proprietary Application Identifier Extension) am Beispiel von "D2  $76\,00\,00\,25\,54\,44\,01\,00$ ":

AID: D2 76 00 00 25 54 44 01 00

RID: D2 76 00 00 25

D: "national registration"

2 76: ISO 3166 Country Code Deutschland

00 00 25: ZKA?

PIX: 54 44 01 00: TAN Anwendung DF \_ TAN

PIX 54440100 vgl. TAN Anwendung DF\_TAN

#### e. GET PROCESSING OPTIONS

Nachfolgend wird das EMV Kommando GET PROCESSING OPTIONS (vgl. z.B. http://blog.saush.com/2006/09/08/getting-information-from-an-emv-chip-card/) abgesetzt; damit wird eine neue Transaktion gestartet.

GET PROCESSING OPTS ohne Parameter 83 00:

| <->  | T=1 Header | APDU                                      | T = 1 |

|------|------------|-------------------------------------------|-------|

|      |            |                                           | XOR   |

| T->C | 00 40 08   | 80 A8 00 00 02 83 00 00                   | E1    |

| T<-C | 00 40 0E   | 77 0A 82 02 18 00 94 04 08 02 04 00 90 00 | A5    |

Aufbau der Antwort (EMV TLV, http://www.emvlab.org/emvtags/all/):

```

77 0A 82 02 18 00 94 04 08 02 04 00

82 Application Interchange Profile: 18 00

Byte 1: bit 8: 1 = Initiate (not supported)

bit 7: 1 = Offline static data authentication is supported

bit 6: 1 = Standard offline dynamic data authentication is supported

bit 5: 1 = Cardholder verification is supported

bit 4: 1 = Terminal Risk Management is to be performed

bit 3: 1 = Issuer Authentication is supported

bit 2: 1 = Combined DDA/AC Generation is supported

bit 1: RFU (0)

Byte 2: RFU ("00")

94 Application File Locator (AFL): 08 02 04 00

Indicates the location (SFI, range of records) of

the AEFs related to a given application

```

#### f. READ RECORD

Kartendaten einlesen, u.A. Kartennummer (wie Geldkarte, http://ftp.ccc.de/docs/cards/geldkarte.pdf)

| <->  | T=1 Header | APDU                                                                          | T=1 XOR |

|------|------------|-------------------------------------------------------------------------------|---------|

| T->C | 00 00 05   | 00 B2 01 BC 00                                                                | 0A      |

| T<-C | 00 00 1A   | 67 MM MM MM NN NN NN NN NN 9D 10 12 06 07 10 02 80 45 55 52 01 3F 00 01 90 00 |         |

#### Antwort der Karte gem. geldkarte.pdf:

```

67 MM MM MM NN NN NN NN NN NN 9D 10 12 06 07 10 02 80 45 55 52 01 3F 00 01

67: Branchenhauptschlüssel

MM MM MM: "Kurz-BLZ" kartenausgebendes Institut

NN NN NN NN NN: individuelle Kartennummer

9D: Prüfziffer über 67 MM MM MN NN NN NN NN

10 12: Verfalldatum der ec-Karte

06 07 10: Aktivierungsdatum der ec-Karte

02 80: Ländercode

45 55 52: Währungskennzeichen "EUR"

01: Wertigkeit der Währung

3F: Freier Zähler für die Schlüsselerzeugung

00 01

```

#### g. SEARCH RECORD IPB

Eine Art Volltextsuche in den Dateien der Karte. Es können keine Spezifikationen dieses Befehls gefunden werden. er ist vermutlich angelehnt an SEARCH RECORD (00 A2) aus der nicht offen gelegten Spezifikation ISO/IEC 7816-9, jedoch sind Informationen aus GSM-Standard ableitbar: CR #0019

Suche nach Tag "9F56" (issuer proprietary bitmap, "Bitfilter" (vgl. Optimised to Fail: Card Readers for Online Banking, Seite 30)

#### SECCOS vor 6.0

| <->  | T=1 Header | APDU                                                                                | T=1 XOR |

|------|------------|-------------------------------------------------------------------------------------|---------|

| T->C | 00 40 0F   | 00 A2 01 0F 09 04 00 CE 9F 56 00 00 00 FF 00                                        | 16      |

| T<-C | 00 40 1E   | 03 70 19 9F 55 01 38 9F 56 12 00 00 03 FF FF 80 00 00 00 00 00 00 00 00 00 00 00 00 | 07      |

#### SECCOS ab 6.0

| <->  | T=1 Header | APDU                                                                                  | T=1 XOR |

|------|------------|---------------------------------------------------------------------------------------|---------|

| T->C | 00 40 0F   | 00 A2 01 0F 09 04 00 CE 9F 56 00 00 00 FF 00                                          | 16      |

| T<-C | 00 40 1E   | 03 70 19 9F 55 01 *00* 9F 56 12 00 00 03 FF FF 80 00 00 00 00 00 00 00 00 00 00 00 00 | 3F      |

#### Antwort der Karte gem. EMV TLV:

```

03 70 19 9F 55 01 38 9F 56 12 00 00 03 FF FF 80 00 00 00 00 00 00 00 00 00 08 00 00

9F 55 01: issuer authentication flag (vermutlich ebenfalls Teil der Speicherstelle?), Länge

38: Wert (00 bei SECCOS ab Version 6.0)

9F 56 12: issuer proprietary bitmap, Länge

00 00 03 FF FF 80 00 00 00 00 00 00 00 00 08 00 00: Wert

```

#### h. SEARCH RECORD CDOL (SECCOS ab 6.0)

b SECCOS Version 06.00 setzt der TAN-Generator einen weiteren SEARCH RECORD-Aufruf für die Suche nach "8C" ab. Das Feld "8C" wird im EMV Standard CDOL1 bezeichnet und legt normalerweise fest, welche Daten dem später folgendem GENERATE AC Kommando übergeben werden sollen.

| <->  | T=1 Header | APDU                                                                                                           | T=1 XOR |

|------|------------|----------------------------------------------------------------------------------------------------------------|---------|

| T->C | 00 0E      | 00 A2 01 0F 08 04 00 CE 8C 00 00 00 FF 00                                                                      |         |

| T<-C | 00 33      | 02 70 2E 8C 21 9F 02 06 9F 03 06 95 05 5F 2A 02 9A 03 9C 01 9F 37 04 9F 4C 08 9F 45 02 9F 33 03 9F 1A 02 9F 35 |         |

|      |            | 01 8D 09 91 10 8A 02 95 05 9F 37 04 90 00                                                                      |         |

Die Antwort enthalt sowohl CDOL1 als auch CDOL2 (letzteres wird üblicherweise für einen zweiten GENERATE AC Aufruf verwendet, dieser entfällt jedoch bei der TAN-Generierung). Aufgeschlüsselt gemäß http://www.emvlab.org/emvtags/all/ ergibt sich folgende Aufstellung. In der Darstellung findet sich vor dem Bindestrich das Feldkennzeichen (Tag), dahinter die Längenangabe.

```

CDOL1 8C 21 9F02-06 Amount, Authorised (Numeric)

1A 29 37 0D 90 46

9F03-06 Amount, Other (Numeric)

F7 A6 6C F7 62 5C

53 25 51 78 4E

95-05 Terminal Verification Results

5F2A-02 Transaction Currency Code

5E 09

9A-03 Transaction Date

64 00 00

9C-01 Transaction Type

0.0

9F37-04 Unpredictable Number

00 00 00 00

9F4C-08 ICC Dynamic Number

00 00 00 00 00 00 00 00

9F45-02 Data Authentication Code

00 00

9F33-03 Terminal Capabilities

00 00 00

9F1A-02 Terminal Country Code

00 00

9F35-01 Terminal Type

CDOL2 8D 09 91-10 Issuer Authentication Data

8A-02 Authorisation Response Code

95-05 Terminal Verification Results

9F37-04 Unpredictable Number

```

Den Beobachtungen nach ist nur die Summe der Längenangaben (hier 0x2B) für das spätere GENERATE AC der TAN-Generierung relevant.

#### i. VERIFY

Der nachfolgende Befehl VERIFY führt i.d.R. eine PIN-Verifikation durch. Bei deutschen Karten wird jedoch darauf verzichtet. Da einem späterem GENERATE AC ein VERIFY-Aufruf vorausgehen muss, wird stellvertretend die Kartennummer (NN NN NN NN NN) übergeben (siehe oben aus READ RECORD).

| <->  | T=1 Header | APDU                    | T=1 XOR |

|------|------------|-------------------------|---------|

| T->C | 00 00 0D   | 80 A8 00 00 02 83 00 00 |         |

| T<-C | 00 00 02   | 90 00                   | 92      |

#### j. HASH

Nach dem Scan und Bestätigung oder Eingabe der Transaktionsdaten (Kontonummer, Betrag) wird in zwei Schritten die eigentliche TAN ermittelt.

Die Transaktionsdaten werden mit ihren Maskenbezeichnungen vorweg aufbereitet und der der Karte übergeben, welche daraus einen Hash errechnet. Auch hier gibt es, ähnlich wie beim Flickercode eine Markierung ob es sich um ASCII (0xE1) und BCD (0xE0) handelt.

| <->  | T=1 Header | APDU                                                                                                           | T=1 XOR |

|------|------------|----------------------------------------------------------------------------------------------------------------|---------|

| T->C | 00 40 3C   | 00 2A 90 A0 36 90 00 80 81 31 E1 53 74 61 72 74 2D 43 6F 64 65 3A E0 87 11 00 03 E1 4B 6F 6E 74 6F 6E 75 6D 6D | CF      |

|      |            | 65 72 E1 33 33 35 35 35 34 E1 42 65 74 72 61 67 E1 31 2C 32 33 B6 00                                           |         |

| T<-C | 00 40 16   | 4B 4E 0A C4 13 E1 9D 4F A9 CA 17 7B 76 D4 AA 0B 5E 42 09 1C 90 00                                              | 28      |

Bezeichnung der "Nutz-Daten" u.U. "VisDataSig"? (vgl. FinTS 3.0 Security Alternative Sicherheitsverfahren, B.5.1): Aufbau:

```

HASH

onummera 3 3 5 5 5 4 ..

00 2A 90 A0 36 90 00 80 81 31 E1 53 74 61 72 74 2D 43 6F 64 65 3A E0 87 11 00 03 E1 4B 6F 6E 74 6F 6E 75 6D 6D 65 72 E1 33 33 35 35 34 ..

.. a B e t r a g a 1 , 2 3 ¶x

.. E1 42 65 74 72 61 67 E1 31 2C 32 33 B6 00

```

#### k. GENERATE AC

Erzeugung des Application Cryptograms. Bei SECCOS vor 6.0 werden 4 Byte des Hashes in eine ansonsten statische Struktur eingebettet übergeben. Ab SECCOS 6.0 wird der komplette Hashwert von 20 Byte verwendet und mit 23 Null-Bytes (0x00) auf insgesamt 0x2B (vgl. oben: SEARCH RECORD CDOL) Bytes aufgefüllt. In das Cryptogram fließen zudem karteninterne Daten/Schlüsselmaterial ein. Die Antwort der Karte ist nicht abhängig von der eingesetzten SECCOS Version.

#### SECCOS vor 6.0

| <->  | T=1 Header | APDU                                                                                                  | T=1 XOR |

|------|------------|-------------------------------------------------------------------------------------------------------|---------|

| T->C | 00 00 31   | 80 AE 00 00 2B 00 00 00 00 00 00 00 00 00 00 00 00 00                                                 | 7B      |

|      |            | 00 00 00 00 20 80 00 00 034 00                                                                        |         |

| T<-C | 00 00 22   | 77 1E 9F 27 01 00 9F 36 02 01 02 9F 26 08 EC F5 0D 2C 1E AF 4E E2 9F 10 07 03 82 01 00 31 00 00 90 00 | 67      |

#### SECCOS ab 6.0

| <->  | T=1 Header | APDU                                                                                                     | T=1 XOR |

|------|------------|----------------------------------------------------------------------------------------------------------|---------|

| T->C | 00 31      | 80 AE 00 00 2B 4B 4E 0A C4 13 E1 9D 4F A9 CA 17 7B 76 D4 AA 0B 5E 42 09 1C 00 00 00 00 00 00 00 00 00 00 |         |

|      |            | 00 00 00 00 00 00 00 00 00 00 00 00 00                                                                   |         |

| T<-C | 00 22      | 77 1E 9F 27 01 00 9F 36 02 01 02 9F 26 08 EC F5 0D 2C 1E AF 4E E2 9F 10 07 03 82 01 00 31 00 00 90 00    |         |

#### Antwort der Karte (EMV TLV):

```

77 1E 9F 27 01 00 9F 36 02 01 02 9F 26 08 EC F5 0D 2C 1E AF 4E E2 9F 10 07 03 82 01 00 31 00 00

77 Response Message Template Format 2

9F 27 Cryptogram Information Data (cid)

00

9F 36 Application Transaction Counter (ATC)

01 02

9F 26 Application Cryptogram (ac)

EC F5 0D 2C 1E AF 4E E2

9F 10 Issuer Application Data

03 82 01 00 31 00 00

```

#### I. Ableitung der TAN

Aus der Antwort der Karte wird nun final die TAN gebildet. Dazu werden die Nutzdaten der GENERATE\_AC-Antworten aneinandergereit und mit dem Bitfilter (IPB) ver-AND-ed:

AND : 1011101100111101010

00000000

000000000

AND : ...

Im Weiteren werden nur noch die Bit-Stellen aus den Daten verwendet, welche im Bit-Filter an korrespondierender Stellen mit 1 gekennzeichnet sind. Es entsteht eine komprimierte Darstellung.

```

Komprimiert: 10111011 0011 11010100

```

Im letzen Schritt werden die letzten acht Bit (LSBs) an den Anfang der Bitfolge gestellt (LEFT ROTATE 8) und die Zahl in Dezimalschreibweise dargestellt.

Damit ist die passende TAN 251067 zur Überweisung gefunden. Das Banksystem kann unter Anwendung der selben Eingangsdaten die TAN verifizieren.

Für Tests und die Verifikation von Vermutungen kam der Smart Card Detective zum Einsatz. Dieser unterstützt leider nur das Protokoll T=0; kann jedoch mit Quellcodemodfikationen zum "blinden" Senden von Kartenantworten an den TAN-Generator verwendet werden. Mit Hilfe des SCD konnte der "Bit-Mix" (IPB-anding, LEFT ROTATE, etc.) aus der Antwort auf GENERATE AC erkannt und rekonstruiert werden.

#### Links / Literatur

- [1] siehe Webseite: http://wiki.ccc-ffm.de/projekte:tangenerator:start#t\_1\_ifsd

- [2] Bild Quelle: Wikimedia Commons

- [3] http://wiki.yobi.be/wiki/Bus\_Pirate#7816-3\_T.3D0\_at\_arbitrary\_baudrate

Kunststoffgehäuse entsprechend Ihrer Zeichnung?

Frontplatten aus Alu für Ihr Gerät?

Gravuren gewünscht?

Ein Möbelstück ganz nach Ihren Vorstellungen?

Günstig und stressfrei?

Wir finden Angebote für die Produktion Ihrer Zeichnungen.

Frästeile aller Art können auf unserer Webseite angefragt werden. Zeichnen Sie direkt im Browser oder laden Sie eigene Daten hoch.

der onlinecad-marktplatz

vww

http://www.cncon.org

e-mail

fly@cncon.org

phone

09122 9242401

# Distance Measurement and Time Synchronization -

#### using Frequency Modulated Continuous Wave (FMCW) Radar

Niko Joram <niko.joram@tu-dresden.de>, Jens Wagner, Axel Strobel, Frank Ellinger

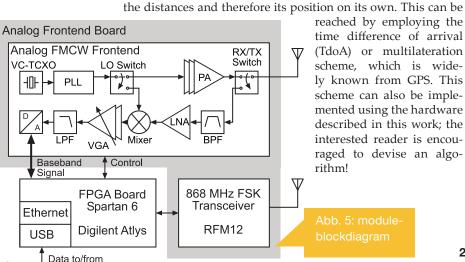

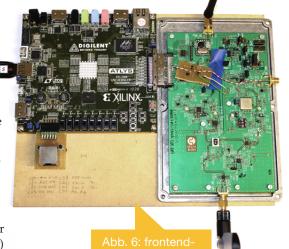

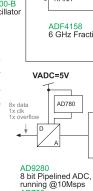

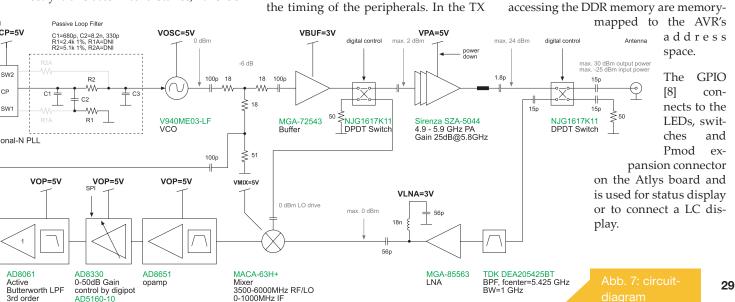

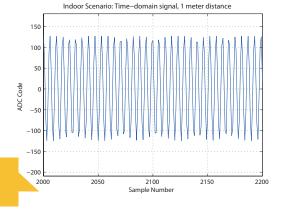

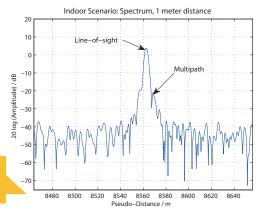

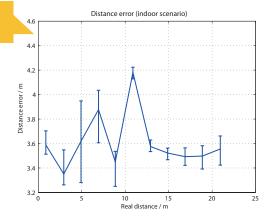

This article presents theory and design of a system for distance measurement and clock synchronization using radio waves with the frequency modulated continuous wave (FMCW) approach. The system consists of a custom analog front-end board and a Digilent Atlys Spartan 6 FPGA board. The analog front-end can transmit and receive frequency chirps in the 5.725 GHz to 5.875 GHz band. Test measurements in an indoor scenario show a maximum distance error of 1.15 m. A useful by-product of the distance calculation is the knowledge of the timing offset between two stations allowing precise wireless time synchronization in the single-digit nanosecond range.

#### Introduction

Nowadays, localization services are needed in many domains, be it the global positioning system GPS or its upcoming European counterpart GALILEO helping vehicle drivers to find their way, or the multiplicity of local positioning systems (LPS) with a variety of different applications. LPS can be found for example in smart factories to locate tools or allow their use only in particular areas, during guided tours in museums or navigation within malls; basically everywhere indoors. This is one of the main advantages in using LPS: the ability to operate in complex environments where GPS fails, like within buildings or areas outside which are densely covered with buildings or where other obstacles cause reflections of the used signals. Determining a 3D position using a LPS can always be traced back to measuring distances between base stations and mobile stations. Because of the fundamental nature of the distance measurement involved, we will present the design and implementation of modules using the frequency-modulated continuous wave (FMCW) radar for ranging, which will certainly find its applications also among hobbyists. The work presented in this article was done in the context of the European research project E-SPONDER [1]. The aim of the project is to provide information

and communication support to first responders (e.g. fire fighters, paramedics) during large scale crisis events. Such events include forest fires, plane crashes or collapsing buildings during earthquakes. Localizing each first responder at all times contributes to the effective management of emergency situations. Since the nature of crises is many-sided, complex environments will certainly be encountered, which is a perfect match for a LPS. In the

following section II, the basics of passive and active FMCW radar systems are described. The design of an analogue front-end and the digital signal processing back-end for an active FMCW system is presented in section III. Finally, some distance measurement results from the designed system are shown in section IV.

Chirp generator

#### **FMCW Basics**

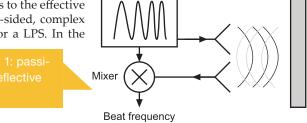

#### a. Passive Reflective Radar

The basic form of FMCW radar may be best known from the automotive sector, where it is used in electronic parking assistants or automatic interval control systems. Figure 1 shows a block diagram. A transceiver sends out a microwave frequency chirp, which propagates approximately with light speed. When the wave reaches an obstacle, it is being reflected and travels back to the transceiver. The signal now has a delay of two times the time-of-flight, measured from the point in time when it was transmitted.

The transceiver receives the reflected signal and mixes it with the transmitting chirp, which is not yet finished (the chirp du-

ration is usually much larger than the expected time-of-flight). The result of the mixing process is a baseband frequency difference signal. In the ideal case of exactly one reflected path, this signal has a single frequency, the so-called beat frequency.

Transmitted chirp Received chirp

To a propagation time

Time

Frequency

It carries the information of how long the signal has travelled until it was received again (i.e. two times the time-of-flight). Figure 2 shows how the propagation time of the chirp signal translates into a beat frequency. The beat frequency is usually detected by performing a Fourier Transform on the baseband signal and using a peak detector to detect the frequency with maximum amplitude.

As already mentioned, if the radio channel does not possess any multipath propagation, this signal has only one frequency component. Multiple signal reflections arriving at the receiver would appear as superimposed frequency components, usually

with lower amplitude and higher frequency, because they take a longer path than the direct line of sight and thus arrive later at the receiver. As a result, multiple peaks with different amplitudes will appear in the spectrum.