# 6 Reset and clock control (RCC)

# 6.1 Reset

There are three types of reset, defined as system reset, power reset and backup domain reset.

# 6.1.1 Power reset

A power reset is generated when one of the following events occurs:

- 1. a Brown-out reset (BOR).

- 2. when exiting from Standby mode.

- 3. when exiting from Shutdown mode.

A Brown-out reset, including power-on or power-down reset (POR/PDR), sets all registers to their reset values except the Backup domain.

When exiting Standby mode, all registers in the V<sub>CORE</sub> domain are set to their reset value. Registers outside the V<sub>CORE</sub> domain (RTC, WKUP, IWDG, and Standby/Shutdown modes control) are not impacted.

When exiting Shutdown mode, a Brown-out reset is generated, resetting all registers except those in the Backup domain.

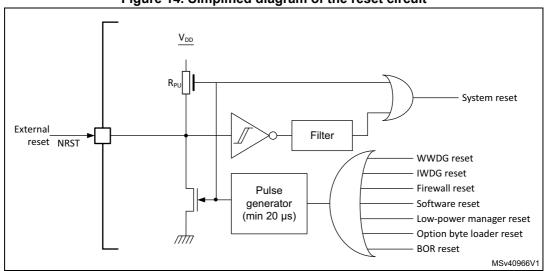

# 6.1.2 System reset

A system reset sets all registers to their reset values unless specified otherwise in the register description.

A system reset is generated when one of the following events occurs:

- 1. A low level on the NRST pin (external reset)

- 2. Window watchdog event (WWDG reset)

- 3. Independent watchdog event (IWDG reset)

- 4. A firewall event (FIREWALL reset)

- 5. A software reset (SW reset) (see Software reset)

- 6. Low-power mode security reset (see *Low-power mode security reset*)

- 7. Option byte loader reset (see Option byte loader reset)

- 8. A Brown-out reset

The reset source can be identified by checking the reset flags in the Control/Status register, RCC\_CSR (see Section 6.4.30: Control/status register (RCC\_CSR)).

These sources act on the NRST pin and it is always kept low during the delay phase. The RESET service routine vector is fixed at address 0x0000\_0004 in the memory map.

The system reset signal provided to the device is output on the NRST pin. The pulse generator guarantees a minimum reset pulse duration of 20  $\mu$ s for each internal reset source. In case of an external reset, the reset pulse is generated while the NRST pin is asserted low.

In case on an internal reset, the internal pull-up  $R_{\rm PU}$  is deactivated in order to save the power consumption through the pull-up resistor.

Figure 14. Simplified diagram of the reset circuit

## Software reset

The SYSRESETREQ bit in Cortex<sup>®</sup>-M4 Application Interrupt and Reset Control Register must be set to force a software reset on the device (refer to the *STM32F3, STM32F4, STM32L4* and *STM32L4*+ Series Cortex<sup>®</sup>-M4 (PM0214)).

## Low-power mode security reset

To prevent that critical applications mistakenly enter a low-power mode, two low-power mode security resets are available. If enabled in option bytes, the resets are generated in the following conditions:

- 1. Entering Standby mode: this type of reset is enabled by resetting nRST\_STDBY bit in User option Bytes. In this case, whenever a Standby mode entry sequence is successfully executed, the device is reset instead of entering Standby mode.

- 2. Entering Stop mode: this type of reset is enabled by resetting nRST\_STOP bit in User option bytes. In this case, whenever a Stop mode entry sequence is successfully executed, the device is reset instead of entering Stop mode.

- 3. Entering Shutdown mode: this type of reset is enabled by resetting nRST\_SHDW bit in User option bytes. In this case, whenever a Shutdown mode entry sequence is successfully executed, the device is reset instead of entering Shutdown mode.

For further information on the User Option Bytes, refer to Section 3.4.1: Option bytes description.

## Option byte loader reset

The option byte loader reset is generated when the OBL\_LAUNCH bit (bit 27) is set in the FLASH\_CR register. This bit is used to launch the option byte loading by software.

# 6.1.3 Backup domain reset

The backup domain has two specific resets.

A backup domain reset is generated when one of the following events occurs:

- 1. Software reset, triggered by setting the BDRST bit in the *Backup domain control register (RCC\_BDCR)*.

- 2. V<sub>DD</sub> or V<sub>BAT</sub> power on, if both supplies have previously been powered off.

A backup domain reset only affects the LSE oscillator, the RTC, the Backup registers and the RCC Backup domain control register.

# 6.2 Clocks

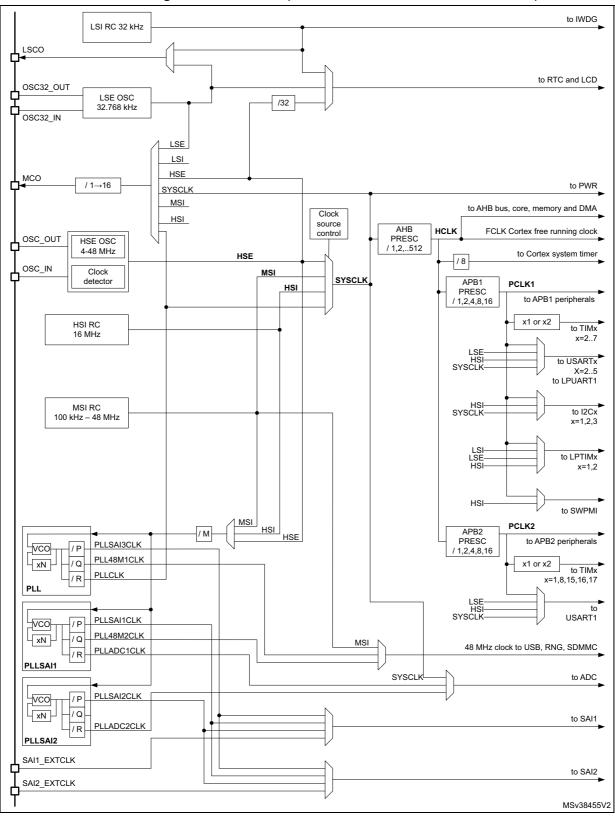

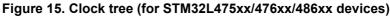

Four different clock sources can be used to drive the system clock (SYSCLK):

- HSI16 (high speed internal)16 MHz RC oscillator clock

- MSI (multispeed internal) RC oscillator clock

- HSE oscillator clock, from 4 to 48 MHz

- PLL clock

The MSI is used as system clock source after startup from Reset, configured at 4 MHz.

The devices have the following additional clock sources:

- 32 kHz low speed internal RC (LSI RC) which drives the independent watchdog and optionally the RTC used for Auto-wakeup from Stop and Standby modes.

- 32.768 kHz low speed external crystal (LSE crystal) which optionally drives the realtime clock (RTCCLK).

- RC 48 MHz internal clock sources (HSI48) to potentially drive the USB FS, the SDMMC and the RNG (only for STM32L496xx/4A6xx devices).

Each clock source can be switched on or off independently when it is not used, to optimize power consumption.

Several prescalers can be used to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB, the APB1 and the APB2 domains is 80 MHz.

All the peripheral clocks are derived from their bus clock (HCLK, PCLK1 or PCLK2) except:

- The 48 MHz clock, used for USB OTG FS, SDMMC and RNG. This clock is derived (selected by software) from one of the four following sources:

- main PLL VCO (PLL48M1CLK)

- PLLSAI1 VCO (PLL48M2CLK)

- MSI clock

- HSI48 internal oscillator (only for STM32L496xx/4A6xx devices)

When the MSI clock is auto-trimmed with the LSE, it can be used by the USB OTG FS device.

When available, the HSI48 48 MHz clock can be coupled to the clock recovery system allowing adequate clock connection for the USB OTG FS (Crystal less solution).

- The ADCs clock which is derived (selected by software) from one of the three following sources:

- system clock (SYSCLK)

- PLLSAI1 VCO (PLLADC1CLK)

- PLLSAI2 VCO (PLLADC2CLK)

- The U(S)ARTs clocks which are derived (selected by software) from one of the four following sources:

- system clock (SYSCLK)

- HSI16 clock

- LSE clock

- APB1 or APB2 clock (PCLK1 or PCLK2 depending on which APB is mapped the U(S)ART)

The wakeup from Stop mode is supported only when the clock is HSI16 or LSE.

- The I<sup>2</sup>Cs clocks which are derived (selected by software) from one of the three following sources:

- system clock (SYSCLK)

- HSI16 clock

- APB1 clock (PCLK1)

The wakeup from Stop mode is supported only when the clock is HSI16.

- The SAI1 and SAI2 clocks which are derived (selected by software) from one of the five following sources:

- an external clock mapped on SAI1\_EXTCLK for SAI1 and SAI2\_EXTCLK for SAI2

- PLLSAI1 VCO (PLLSAI1CLK)

- PLLSAI2 VCO (PLLSAI2CLK)

- main PLL VCO (PLLSAI3CLK)

- HSI16 clock (only for STM32L496xx/4A6xx devices)

- The SWPMI1 clock which is derived (selected by software) from one of the two following sources:

- HSI16 clock

- APB1 clock (PCLK1)

- The wakeup from Stop mode is supported only when the clock is HSI16.

- The low-power timers (LPTIMx) clock which are derived (selected by software) from one of the five following sources:

- LSI clock

- LSE clock

- HSI16 clock

- APB1 clock (PCLK1)

- External clock mapped on LPTIMx\_IN1

The functionality in Stop mode (including wakeup) is supported only when the clock is LSI or LSE, or in external clock mode.

- The RTC and LCD clock which is derived (selected by software) from one of the three following sources:

- LSE clock

- LSI clock

- HSE clock divided by 32

The functionality in Stop mode (including wakeup) is supported only when the clock is LSI or LSE.

• The IWDG clock which is always the LSI clock.

The RCC feeds the Cortex<sup>®</sup> System Timer (SysTick) external clock with the AHB clock (HCLK) divided by 8. The SysTick can work either with this clock or directly with the Cortex<sup>®</sup> clock (HCLK), configurable in the SysTick Control and Status Register.

FCLK acts as Cortex<sup>®</sup>-M4 free-running clock. For more details refer to the *STM32F3*, *STM32F4*, *STM32L4* and *STM32L4*+ *Series Cortex*<sup>®</sup>-M4 programming manual (PM0214).

- 1. For full details about the internal and external clock source characteristics, please refer to the "Electrical characteristics" section in your device datasheet.

- 2. The ADC clock can be derived from the AHB clock of the ADC bus interface, divided by a programmable factor (1, 2 or 4). When the programmable factor is '1', the AHB prescaler must be equal to '1'.

Figure 16. Clock tree (for STM32L496xx/4A6xx devices)

# 6.2.1 HSE clock

The high speed external clock signal (HSE) can be generated from two possible clock sources:

- HSE external crystal/ceramic resonator

- HSE user external clock

The resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

| Clock source                  | Hardware configuration                                                                                                                                                                       |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External clock                | OSC_IN OSC_OUT                                                                                                                                                                               |

| Crystal/Ceramic<br>resonators | $\begin{array}{c c} OSC_{IN} OSC_{OUT} \\ \hline \\ \hline \\ \hline \\ \hline \\ \hline \\ \hline \\ \\ \hline \\ \\ \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ |

Figure 17. HSE/ LSE clock sources

## External crystal/ceramic resonator (HSE crystal)

The 4 to 48 MHz external oscillator has the advantage of producing a very accurate rate on the main clock.

The associated hardware configuration is shown in *Figure 17*. Refer to the electrical characteristics section of the *datasheet* for more details.

The HSERDY flag in the *Clock control register (RCC\_CR)* indicates if the HSE oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in the *Clock interrupt enable register (RCC\_CIER)*.

The HSE Crystal can be switched on and off using the HSEON bit in the *Clock control register (RCC\_CR)*.

#### External source (HSE bypass)

In this mode, an external clock source must be provided. It can have a frequency of up to 48 MHz. You select this mode by setting the HSEBYP and HSEON bits in the *Clock control register (RCC\_CR)*. The external clock signal (square, sinus or triangle) with ~40-60 % duty cycle depending on the frequency (refer to the datasheet) has to drive the OSC\_IN pin while the OSC\_OUT pin can be used a GPIO. See *Figure 17*.

## 6.2.2 HSI16 clock

The HSI16 clock signal is generated from an internal 16 MHz RC Oscillator.

The HSI16 RC oscillator has the advantage of providing a clock source at low cost (no external components). It also has a faster startup time than the HSE crystal oscillator however, even with calibration the frequency is less accurate than an external crystal oscillator or ceramic resonator.

The HSI16 clock can be selected as system clock after wakeup from Stop modes (Stop 0, Stop 1 or Stop 2). Refer to *Section 6.3: Low-power modes*. It can also be used as a backup clock source (auxiliary clock) if the HSE crystal oscillator fails. Refer to *Section 6.2.10: Clock security system (CSS)*.

## Calibration

RC oscillator frequencies can vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated by ST for 1 % accuracy at  $T_A=25^{\circ}C$ .

After reset, the factory calibration value is loaded in the HSICAL[7:0] bits in the *Internal clock sources calibration register (RCC\_ICSCR)*.

If the application is subject to voltage or temperature variations this may affect the RC oscillator speed. You can trim the HSI16 frequency in the application using the HSITRIM[4:0] bits (or HSITRIM[6:0] on STM32L496xx/4A6xx devices) in the *Internal clock sources calibration register (RCC\_ICSCR)*.

For more details on how to measure the HSI16 frequency variation, refer to Section 6.2.18: Internal/external clock measurement with TIM15/TIM16/TIM17.

The HSIRDY flag in the *Clock control register (RCC\_CR)* indicates if the HSI16 RC is stable or not. At startup, the HSI16 RC output clock is not released until this bit is set by hardware.

The HSI16 RC can be switched on and off using the HSION bit in the *Clock control register* (*RCC\_CR*).

The HSI16 signal can also be used as a backup source (Auxiliary clock) if the HSE crystal oscillator fails. Refer to Section 6.2.10: Clock security system (CSS) on page 216.

# 6.2.3 MSI clock

The MSI clock signal is generated from an internal RC oscillator. Its frequency range can be adjusted by software by using the MSIRANGE[3:0] bits in the *Clock control register* (*RCC\_CR*). Twelve frequency ranges are available: 100 kHz, 200 kHz, 400 kHz, 800 kHz, 1 MHz, 2 MHz, 4 MHz (default value), 8 MHz, 16 MHz, 24 MHz, 32 MHz and 48 MHz.

The MSI clock is used as system clock after restart from Reset, wakeup from Standby and Shutdown low-power modes. After restart from Reset, the MSI frequency is set to its default value 4 MHz. Refer to *Section 6.3: Low-power modes*.

The MSI clock can be selected as system clock after a wakeup from Stop mode (Stop 0, Stop 1 or Stop 2). Refer to *Section 6.3: Low-power modes*. It can also be used as a backup clock source (auxiliary clock) if the HSE crystal oscillator fails. Refer to *Section 6.2.10: Clock security system (CSS)*.

The MSI RC oscillator has the advantage of providing a low-cost (no external components) low-power clock source. In addition, when used in PLL-mode with the LSE, it provides a very accurate clock source which can be used by the USB OTG FS device, and feed the main PLL to run the system at the maximum speed 80 MHz.

The MSIRDY flag in the *Clock control register (RCC\_CR)* indicates wether the MSI RC is stable or not. At startup, the MSI RC output clock is not released until this bit is set by hardware. The MSI RC can be switched on and off by using the MSION bit in the *Clock control register (RCC\_CR)*.

## Hardware auto calibration with LSE (PLL-mode)

When a 32.768 kHz external oscillator is present in the application, it is possible to configure the MSI in a PLL-mode by setting the MSIPLLEN bit in the *Clock control register (RCC\_CR)*. When configured in PLL-mode, the MSI automatically calibrates itself thanks to the LSE. This mode is available for all MSI frequency ranges. At 48 MHz, the MSI in PLL-mode can be used for the USB OTG FS device, saving the need of an external high-speed crystal.

## Software calibration

The MSI RC oscillator frequency can vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated by ST for 1 % accuracy at an ambient temperature, TA, of 25 °C. After reset, the factory calibration value is loaded in the MSICAL[7:0] bits in the *Internal clock sources calibration register (RCC\_ICSCR)*. If the application is subject to voltage or temperature variations, this may affect the RC oscillator speed. You can trim the MSI frequency in the application by using the MSITRIM[7:0] bits in the RCC\_ICSCR register. For more details on how to measure the MSI frequency variation please refer to *Section 6.2.18: Internal/external clock measurement with TIM15/TIM16/TIM17*.

## 6.2.4 HSI48 clock (only valid for STM32L496xx/4A6xx devices)

The HSI48 clock signal is generated from an internal 48 MHz RC oscillator and can be used directly for USB and for random number generator (RNG) as well as SDMMC.

The internal 48 MHz RC oscillator is mainly dedicated to provide a high precision clock to the USB peripheral by means of a special Clock Recovery System (CRS) circuitry. The CRS

RM0351 Rev 6

can use the USB SOF signal, the LSE or an external signal to automatically and quickly adjust the oscillator frequency on-fly. It is disabled as soon as the system enters Stop or Standby mode. When the CRS is not used, the HSI48 RC oscillator runs on its default frequency which is subject to manufacturing process variations.

For more details on how to configure and use the CRS peripheral please refer to Section 7: Clock recovery system (CRS) (only valid for STM32L496xx/4A6xx devices).

The HSI48RDY flag in the Clock recovery RC register (RCC\_CRRCR) indicates whether the HSI48 RC oscillator is stable or not. At startup, the HSI48 RC oscillator output clock is not released until this bit is set by hardware.

The HSI48 can be switched on and off using the HSI48ON bit in the Clock recovery RC register (RCC\_CRRCR).

# 6.2.5 PLL

The device embeds 3 PLLs: PLL, PLLSAI1, PLLSAI2. Each PLL provides up to three independent outputs. The internal PLLs can be used to multiply the HSI16, HSE or MSI output clock frequency. The PLLs input frequency must be between 4 and 16 MHz. The selected clock source is divided by a programmable factor PLLM from 1 to 8 to provide a clock frequency in the requested input range. Refer to *Figure 15: Clock tree (for STM32L475xx/476xx/486xx devices)* and *Figure 16: Clock tree (for STM32L496xx/4A6xx devices)* and *PLL configuration register (RCC\_PLLCFGR)*.

The PLLs configuration (selection of the input clock and multiplication factor) must be done before enabling the PLL. Once the PLL is enabled, these parameters cannot be changed.

To modify the PLL configuration, proceed as follows:

- 1. Disable the PLL by setting PLLON to 0 in *Clock control register (RCC\_CR)*.

- 2. Wait until PLLRDY is cleared. The PLL is now fully stopped.

- 3. Change the desired parameter.

- 4. Enable the PLL again by setting PLLON to 1.

- 5. Enable the desired PLL outputs by configuring PLLPEN, PLLQEN, PLLREN in *PLL configuration register (RCC\_PLLCFGR)*.

An interrupt can be generated when the PLL is ready, if enabled in the *Clock interrupt enable register (RCC\_CIER)*.

The same procedure is applied for changing the configuration of the PLLSAI1 or PLLSAI2:

- 1. Disable the PLLSAI1/PLLSAI2 by setting PLLSAI1ON/PLLSAI2ON to 0 in *Clock control register (RCC\_CR)*.

- 2. Wait until PLLSAI1RDY/PLLSAI2RDY is cleared. The PLLSAI1/PLLSAI2 is now fully stopped.

- 3. Change the desired parameter.

- 4. Enable the PLLSAI1/PLLSAI2 again by setting PLLSAI1ON/PLLSAI2ON to 1.

- Enable the desired PLL outputs by configuring PLLSAI1PEN/PLLSAI2PEN, PLLSAI1QEN/PLLSAI2QEN, PLLSAI1REN/PLLSAI2REN in *PLLSAI1 configuration* register (RCC\_PLLSAI1CFGR) and *PLLSAI2 configuration register* (RCC\_PLLSAI2CFGR).

The PLL output frequency must not exceed 80 MHz.

The enable bit of each PLL output clock (PLLPEN, PLLQEN, PLLREN, PLLSAI1PEN, PLLSAI1QEN, PLLSAI1REN, PLLSAI2PEN and PLLSAI2REN) can be modified at any time without stopping the corresponding PLL. PLLREN cannot be cleared if PLLCLK is used as system clock.

# 6.2.6 LSE clock

The LSE crystal is a 32.768 kHz Low Speed External crystal or ceramic resonator. It has the advantage of providing a low-power but highly accurate clock source to the real-time clock peripheral (RTC) for clock/calendar or other timing functions.

The LSE crystal is switched on and off using the LSEON bit in *Backup domain control register (RCC\_BDCR)*. The crystal oscillator driving strength can be changed at runtime using the LSEDRV[1:0] bits in the *Backup domain control register (RCC\_BDCR)* to obtain the best compromise between robustness and short start-up time on one side and low-power-consumption on the other side. The LSE drive can be decreased to the lower drive capability (LSEDRV=00) when the LSE is ON. However, once LSEDRV is selected, the drive capability can not be increased if LSEON=1.

The LSERDY flag in the *Backup domain control register (RCC\_BDCR)* indicates whether the LSE crystal is stable or not. At startup, the LSE crystal output clock signal is not released until this bit is set by hardware. An interrupt can be generated if enabled in the *Clock interrupt enable register (RCC\_CIER)*.

## External source (LSE bypass)

In this mode, an external clock source must be provided. It can have a frequency of up to 1 MHz. You select this mode by setting the LSEBYP and LSEON bits in the *AHB1 peripheral clocks enable in Sleep and Stop modes register (RCC\_AHB1SMENR)*. The external clock signal (square, sinus or triangle) with ~50 % duty cycle has to drive the OSC32\_IN pin while the OSC32\_OUT pin can be used as GPIO. See *Figure 17*.

# 6.2.7 LSI clock

The LSI RC acts as a low-power clock source that can be kept running in Stop and Standby mode for the independent watchdog (IWDG), RTC and LCD. The clock frequency is 32 kHz. For more details, refer to the electrical characteristics section of the datasheets.

The LSI RC can be switched on and off using the LSION bit in the *Control/status register* (RCC\_CSR).

The LSIRDY flag in the *Control/status register (RCC\_CSR)* indicates if the LSI oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in the *Clock interrupt enable register (RCC\_CIER)*.

# 6.2.8 System clock (SYSCLK) selection

Four different clock sources can be used to drive the system clock (SYSCLK):

- MSI oscillator

- HSI16 oscillator

- HSE oscillator

- PLL

The system clock maximum frequency is 80 MHz. After a system reset, the MSI oscillator, at 4 MHz, is selected as system clock. When a clock source is used directly or through the PLL as a system clock, it is not possible to stop it.

A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay or PLL locked). If a clock source which is not yet ready is selected, the switch will occur when the clock source becomes ready. Status bits in the *Internal clock sources calibration register (RCC\_ICSCR)* indicate which clock(s) is (are) ready and which clock is currently used as a system clock.

# 6.2.9 Clock source frequency versus voltage scaling

The following table gives the different clock source frequencies depending on the product voltage range.

| Product voltage        |              | Clo    | ck frequency |                               |

|------------------------|--------------|--------|--------------|-------------------------------|

| range                  | MSI          | HSI16  | HSE          | PLL/PLLSAI1/PLLSAI2           |

| Range 1 <sup>(1)</sup> | 48 MHz       | 16 MHz | 48 MHz       | 80 MHz<br>(VCO max = 344 MHz) |

| Range 2 <sup>(2)</sup> | 24 MHz range | 16 MHz | 26 MHz       | 26 MHz<br>(VCO max = 128 MHz) |

Table 33. Clock source frequency

1. Also for SMPS Range1 and SMPS Range2 High

2. Also for SMPS Range2 Low

# 6.2.10 Clock security system (CSS)

Clock Security System can be activated by software. In this case, the clock detector is enabled after the HSE oscillator startup delay, and disabled when this oscillator is stopped.

If a failure is detected on the HSE clock, the HSE oscillator is automatically disabled, a clock failure event is sent to the break input of the advanced-control timers (TIM1/TIM8 and TIM15/16/17) and an interrupt is generated to inform the software about the failure (Clock Security System Interrupt CSSI), allowing the MCU to perform rescue operations. The CSSI is linked to the Cortex<sup>®</sup>-M4 NMI (Non-Maskable Interrupt) exception vector.

Note: Once the CSS is enabled and if the HSE clock fails, the CSS interrupt occurs and a NMI is automatically generated. The NMI will be executed indefinitely unless the CSS interrupt pending bit is cleared. As a consequence, in the NMI ISR user must clear the CSS interrupt by setting the CSSC bit in the Clock interrupt clear register (RCC\_CICR).

If the HSE oscillator is used directly or indirectly as the system clock (indirectly means: it is used as PLL input clock, and the PLL clock is used as system clock), a detected failure causes a switch of the system clock to the MSI or the HSI16 oscillator depending on the STOPWUCK configuration in the *Clock configuration register (RCC\_CFGR)*, and the disabling of the HSE oscillator. If the HSE clock (divided or not) is the clock entry of the PLL used as system clock when the failure occurs, the PLL is disabled too.

# 6.2.11 Clock security system on LSE

A Clock Security System on LSE can be activated by software writing the LSECSSON bit in the *Backup domain control register (RCC\_BDCR)*. This bit can be disabled only by a hardware reset or RTC software reset, or after a failure detection on LSE. LSECSSON must be written after LSE and LSI are enabled (LSEON and LSION enabled) and ready (LSERDY and LSIRDY set by hardware), and after the RTC clock has been selected by RTCSEL.

The CSS on LSE is working in all modes except VBAT. It is working also under system reset (excluding power on reset). If a failure is detected on the external 32 kHz oscillator, the LSE clock is no longer supplied to the RTC but no hardware action is made to the registers. If the MSI was in PLL-mode, this mode is disabled.

In Standby mode a wakeup is generated. In other modes an interrupt can be sent to wakeup the software (see *Clock interrupt enable register (RCC\_CIER)*, *Clock interrupt flag register (RCC\_CIFR)*, *Clock interrupt clear register (RCC\_CICR)*).

The software MUST then disable the LSECSSON bit, stop the defective 32 kHz oscillator (disabling LSEON), and change the RTC clock source (no clock or LSI or HSE, with RTCSEL), or take any required action to secure the application.

The frequency of LSE oscillator have to be higher than 30 kHz to avoid false positive CSS detection.

# 6.2.12 USB Clock

The USB clock can be derived from either:

- The RC 48 MHz (HSI48) clock (only for STM32L496xx/4A6xx devices)

- The MSI clock when auto-trimmed by the LSE

The HSI48 48 MHz clock can be coupled to the clock recovery system allowing adequate clock connection for the USB OTG FS in device mode (removing the need for an external high speed or low speed crystal).

The MSI clock when auto-trimmed by the LSE, can provide a very accurate clock source which can be used by the USB OTG FS in device mode (removing the need for an external high speed crystal).

# 6.2.13 ADC clock

The ADC clock is derived from the system clock, or from the PLLSAI1 or the PLLSAI2 output. It can reach 80 MHz and can be divided by the following prescalers values: 1,2,4,6,8,10,12,16,32,64,128 or 256 by configuring the ADC123\_CCR register. It is asynchronous to the AHB clock. Alternatively, the ADC clock can be derived from the AHB clock of the ADC bus interface, divided by a programmable factor (1, 2 or 4). This programmable factor is configured using the CKMODE bit fields in the ADC123\_CCR.

If the programmed factor is '1', the AHB prescaler must be set to '1'.

## 6.2.14 RTC clock

The RTCCLK clock source can be either the HSE/32, LSE or LSI clock. It is selected by programming the RTCSEL[1:0] bits in the *Backup domain control register (RCC\_BDCR)*. This selection cannot be modified without resetting the Backup domain. The system must always be configured so as to get a PCLK frequency greater then or equal to the RTCCLK frequency for a proper operation of the RTC.

RM0351 Rev 6

The LSE clock is in the Backup domain, whereas the HSE and LSI clocks are not. Consequently:

- If LSE is selected as RTC clock:

- The RTC continues to work even if the  $V_{DD}$  supply is switched off, provided the  $V_{BAT}$  supply is maintained.

- If LSI is selected as the RTC clock:

- The RTC state is not guaranteed if the V<sub>DD</sub> supply is powered off.

- If the HSE clock divided by a prescaler is used as the RTC clock:

- The RTC state is not guaranteed if the V<sub>DD</sub> supply is powered off or if the internal voltage regulator is powered off (removing power from the V<sub>CORE</sub> domain).

When the RTC clock is LSE or LSI, the RTC remains clocked and functional under system reset.

## 6.2.15 Timer clock

The timer clock frequencies are automatically defined by hardware. There are two cases:

- 1. If the APB prescaler equals 1, the timer clock frequencies are set to the same frequency as that of the APB domain.

- 2. Otherwise, they are set to twice (×2) the frequency of the APB domain.

# 6.2.16 Watchdog clock

If the Independent watchdog (IWDG) is started by either hardware option or software access, the LSI oscillator is forced ON and cannot be disabled. After the LSI oscillator temporization, the clock is provided to the IWDG.

## 6.2.17 Clock-out capability

MCO

The microcontroller clock output (MCO) capability allows the clock to be output onto the external MCO pin. One of eight clock signals can be selected as the MCO clock.

- LSI

- LSE

- SYSCLK

- HSI16

- HSI48 (for STM32L496xx/4A6xx devices)

- HSE

- PLLCLK

- MSI

The selection is controlled by the MCOSEL[2:0] (or MCOSEL[3:0] for STM32L496xx/4A6xx devices) bits of the *Clock configuration register (RCC\_CFGR)*.

The selected clock can be divided with the MCOPRE[2:0] field of the *Clock* configuration register (RCC\_CFGR).

LSCO

Another output (LSCO) allows a low speed clock to be output onto the external LSCO pin:

- LSI

- LSE

This output remains available in Stop (Stop 0, Stop 1 and Stop 2) and Standby modes. The selection is controlled by the LSCOSEL, and enabled with the LSCOEN in the *Backup domain control register (RCC\_BDCR)*.

The MCO clock output requires the corresponding alternate function selected on the MCO pin, the LSCO pin should be left in default POR state.

## 6.2.18 Internal/external clock measurement with TIM15/TIM16/TIM17

It is possible to indirectly measure the frequency of all on-board clock sources by mean of the TIM15, TIM16 or TIM17 channel 1 input capture, as represented on *Figure 18, Figure 19* and *Figure 20*.

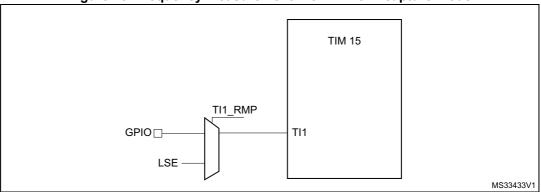

Figure 18. Frequency measurement with TIM15 in capture mode

The input capture channel of the Timer 15 can be a GPIO line or an internal clock of the MCU. This selection is performed through the TI1\_RMP bit in the TIM15\_OR register. The possibilities are the following ones:

- TIM15 Channel1 is connected to the GPIO. Refer to the alternate function mapping in the device datasheets.

- TIM15 Channel1 is connected to the LSE.

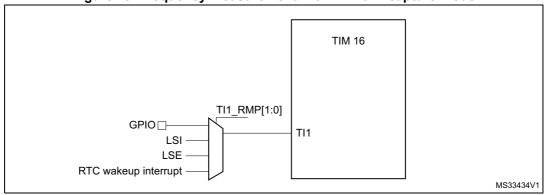

Figure 19. Frequency measurement with TIM16 in capture mode

The input capture channel of the Timer 16 can be a GPIO line or an internal clock of the MCU. This selection is performed through the TI1\_RMP[1:0] bits in the TIM16\_OR register. The possibilities are the following ones:

- TIM16 Channel1 is connected to the GPIO. Refer to the alternate function mapping in the device datasheets.

- TIM16 Channel1 is connected to the LSI clock.

- TIM16 Channel1 is connected to the LSE clock.

- TIM16 Channel1 is connected to the RTC wakeup interrupt signal. In this case the RTC interrupt should be enabled.

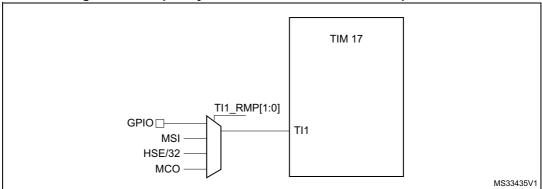

## Figure 20. Frequency measurement with TIM17 in capture mode

The input capture channel of the Timer 17 can be a GPIO line or an internal clock of the MCU. This selection is performed through the TI1\_RMP[1:0] bits in the TIM17\_OR register. The possibilities are the following ones:

- TIM17 Channel1 is connected to the GPIO. Refer to the alternate function mapping in the device datasheets.

- TIM17 Channel1 is connected to the MSI Clock.

- TIM17 Channel1 is connected to the HSE/32 Clock.

- TIM17 Channel1 is connected to the microcontroller clock output (MCO), this selection is controlled by the MCO[2:0] (or MCOSEL[3:0] for STM32L496xx/4A6xx devices) bits of the Clock configuration register (RCC\_CFGR).

## Calibration of the HSI16 and the MSI

For TIM15 and TIM16, the primary purpose of connecting the LSE to the channel 1 input capture is to be able to precisely measure the HSI16 and MSI system clocks (for this, either the HSI16 or MSI should be used as the system clock source). The number of HSI16 (MSI, respectively) clock counts between consecutive edges of the LSE signal provides a measure of the internal clock period. Taking advantage of the high precision of LSE crystals (typically a few tens of ppm's), it is possible to determine the internal clock frequency with the same resolution, and trim the source to compensate for manufacturing, process, temperature and/or voltage related frequency deviations.

The MSI and HSI16 oscillator both have dedicated user-accessible calibration bits for this purpose.

The basic concept consists in providing a relative measurement (e.g. the HSI16/LSE ratio): the precision is therefore closely related to the ratio between the two clock sources. The higher the ratio is, the better the measurement will be.

If LSE is not available, HSE/32 will be the better option in order to reach the most precise calibration possible.

It is however not possible to have a good enough resolution when the MSI clock is low (typically below 1 MHz). In this case, it is advised to:

- accumulate the results of several captures in a row

- use the timer's input capture prescaler (up to 1 capture every 8 periods)

- use the RTC wakeup interrupt signal (when the RTC is clocked by the LSE) as the input for the channel1 input capture. This improves the measurement precision. For this purpose the RTC wakeup interrupt must be enable.

## Calibration of the LSI

The calibration of the LSI will follow the same pattern that for the HSI16, but changing the reference clock. It will be necessary to connect LSI clock to the channel 1 input capture of the TIM16. Then define the HSE as system clock source, the number of his clock counts between consecutive edges of the LSI signal provides a measure of the internal low speed clock period.

The basic concept consists in providing a relative measurement (e.g. the HSE/LSI ratio): the precision is therefore closely related to the ratio between the two clock sources. The higher the ratio is, the better the measurement will be.

# 6.2.19 Peripheral clock enable register (RCC\_AHBxENR, RCC\_APBxENRy)

Each peripheral clock can be enabled by the xxxxEN bit of the RCC\_AHBxENR, RCC\_APBxENRy registers.

When the peripheral clock is not active, the peripheral registers read or write accesses are not supported.

The enable bit has a synchronization mechanism to create a glitch free clock for the peripheral. After the enable bit is set, there is a 2 clock cycles delay before the clock be active.

**Caution:** Just after enabling the clock for a peripheral, software must wait for a delay before accessing the peripheral registers.

# 6.3 Low-power modes

- AHB and APB peripheral clocks, including DMA clock, can be disabled by software.

- Sleep and Low Power Sleep modes stops the CPU clock. The memory interface clocks (Flash and SRAM1 and SRAM2 interfaces) can be stopped by software during sleep mode. The AHB to APB bridge clocks are disabled by hardware during Sleep mode when all the clocks of the peripherals connected to them are disabled.

- Stop modes (Stop 0, Stop 1 and Stop 2) stops all the clocks in the V<sub>CORE</sub> domain and disables the three PLL, the HSI16, the MSI and the HSE oscillators.

All U(S)ARTs, LPUARTs and I<sup>2</sup>Cs have the capability to enable the HSI16 oscillator

even when the MCU is in Stop mode (if HSI16 is selected as the clock source for that peripheral).

All U(S)ARTs and LPUARTs can also be driven by the LSE oscillator when the system is in Stop mode (if LSE is selected as clock source for that peripheral) and the LSE oscillator is enabled (LSEON). In that case the LSE remains always ON in Stop mode (they do not have the capability to turn on the LSE oscillator).

Standby and Shutdown modes stops all the clocks in the V<sub>CORE</sub> domain and disables the PLL, the HSI16, the MSI and the HSE oscillators.

The CPU's deepsleep mode can be overridden for debugging by setting the DBG\_STOP or DBG\_STANDBY bits in the DBGMCU\_CR register.

When leaving the Stop modes (Stop 0, Stop 1 or Stop 2), the system clock is either MSI or HSI16, depending on the software configuration of the STOPWUCK bit in the RCC\_CFGR register. The frequency (range and user trim) of the MSI oscillator is the one configured before entering Stop mode. The user trim of HSI16 is kept. If the MSI was in PLL-mode before entering Stop mode, the PLL-mode stabilization time must be waited for after wakeup even if the LSE was kept ON during the Stop mode.

When leaving the Standby and Shutdown modes, the system clock is MSI. The MSI frequency at wakeup from Standby mode is configured with the MSISRANGE is the RCC\_CSR register, from 1 to 8 MHz. The MSI frequency at wakeup from Shutdown mode is 4 MHz. The user trim is lost.

If a Flash memory programming operation is on going, Stop, Standby and Shutdown modes entry is delayed until the Flash memory interface access is finished. If an access to the APB domain is ongoing, Stop, Standby and Shutdown modes entry is delayed until the APB access is finished.

# 6.4 RCC registers

# 6.4.1 Clock control register (RCC\_CR)

## Address offset: 0x00

Reset value: 0x0000 0063. HSEBYP is cleared upon power-on reset. It is not affected upon other types of reset.

Access: no wait state, word, half-word and byte access

| 31   | 30   | 29                 | 28                | 27                 | 26                | 25           | 24    | 23   | 22     | 21       | 20   | 19           | 18           | 17         | 16        |

|------|------|--------------------|-------------------|--------------------|-------------------|--------------|-------|------|--------|----------|------|--------------|--------------|------------|-----------|

| Res. | Res. | PLL<br>SAI2<br>RDY | PLL<br>SAI2<br>ON | PLL<br>SAI1<br>RDY | PLL<br>SAI1<br>ON | PLL<br>RDY   | PLLON | Res. | Res.   | Res.     | Res. | CSS<br>ON    | HSE<br>BYP   | HSE<br>RDY | HSE<br>ON |

|      |      | r                  | rw                | r                  | rw                | r            | rw    |      |        |          |      | rs           | rw           | r          | rw        |

| 15   | 14   | 13                 | 12                | 11                 | 10                | 9            | 8     | 7    | 6      | 5        | 4    | 3            | 2            | 1          | 0         |

| Res. | Res. | Res.               | Res.              | HSI<br>ASFS        | HSI<br>RDY        | HSI<br>KERON | HSION |      | MSIRAN | IGE[3:0] |      | MSI<br>RGSEL | MSI<br>PLLEN | MSI<br>RDY | MSION     |

|      |      |                    |                   | rw                 | r                 | rw           | rw    | rw   | rw     | rw       | rw   | rs           | rw           | r          | rw        |

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 PLLSAI2RDY: SAI2 PLL clock ready flag

Set by hardware to indicate that the PLLSAI2 is locked.

- 0: PLLSAI2 unlocked

- 1: PLLSAI2 locked

- Bit 28 PLLSAI2ON: SAI2 PLL enable

Set and cleared by software to enable PLLSAI2. Cleared by hardware when entering Stop, Standby or Shutdown mode. 0: PLLSAI2 OFF 1: PLLSAI2 ON

#### Bit 27 **PLLSAI1RDY**: SAI1 PLL clock ready flag

Set by hardware to indicate that the PLLSAI1 is locked.

0: PLLSAI1 unlocked

1: PLLSAI1 locked

Bit 26 PLLSAI1ON: SAI1 PLL enable

Set and cleared by software to enable PLLSAI1. Cleared by hardware when entering Stop, Standby or Shutdown mode. 0: PLLSAI1 OFF 1: PLLSAI1 ON

## Bit 25 PLLRDY: Main PLL clock ready flag

Set by hardware to indicate that the main PLL is locked. 0: PLL unlocked 1: PLL locked

# Bit 24 PLLON: Main PLL enable

Set and cleared by software to enable the main PLL.

Cleared by hardware when entering Stop, Standby or Shutdown mode. This bit cannot be reset if the PLL clock is used as the system clock. 0: PLL OFF 1: PLL ON

RM0351 Rev 6

Bits 23:20 Reserved, must be kept at reset value.

Bit 19 **CSSON**: Clock security system enable

Set by software to enable the clock security system. When CSSON is set, the clock detector is enabled by hardware when the HSE oscillator is ready, and disabled by hardware if a HSE clock failure is detected. This bit is set only and is cleared by reset.

0: Clock security system OFF (clock detector OFF)

1: Clock security system ON (Clock detector ON if the HSE oscillator is stable, OFF if not).

#### Bit 18 HSEBYP: HSE crystal oscillator bypass

Set and cleared by software to bypass the oscillator with an external clock. The external clock must be enabled with the HSEON bit set, to be used by the device. The HSEBYP bit can be written only if the HSE oscillator is disabled.

0: HSE crystal oscillator not bypassed

1: HSE crystal oscillator bypassed with external clock

#### Bit 17 HSERDY: HSE clock ready flag

Set by hardware to indicate that the HSE oscillator is stable.

0: HSE oscillator not ready

1: HSE oscillator ready

Note: Once the HSEON bit is cleared, HSERDY goes low after 6 HSE clock cycles.

#### Bit 16 HSEON: HSE clock enable

Set and cleared by software.

Cleared by hardware to stop the HSE oscillator when entering Stop, Standby or Shutdown mode. This bit cannot be reset if the HSE oscillator is used directly or indirectly as the system clock.

0: HSE oscillator OFF

1: HSE oscillator ON

- Bits 15:12 Reserved, must be kept at reset value.

- Bit 11 HSIASFS: HSI16 automatic start from Stop

Set and cleared by software. When the system wakeup clock is MSI, this bit is used to wakeup the HSI16 is parallel of the system wakeup.

0: HSI16 oscillator is not enabled by hardware when exiting Stop mode with MSI as wakeup clock.

1: HSI16 oscillator is enabled by hardware when exiting Stop mode with MSI as wakeup clock.

Bit 10 HSIRDY: HSI16 clock ready flag

Set by hardware to indicate that HSI16 oscillator is stable. This bit is set only when HSI16 is enabled by software by setting HSION.

- 0: HSI16 oscillator not ready

- 1: HSI16 oscillator ready

Note: Once the HSION bit is cleared, HSIRDY goes low after 6 HSI16 clock cycles.

Bit 9 HSIKERON: HSI16 always enable for peripheral kernels.

Set and cleared by software to force HSI16 ON even in Stop modes. The HSI16 can only feed USARTs and I<sup>2</sup>Cs peripherals configured with HSI16 as kernel clock. Keeping the HSI16 ON in Stop mode allows to avoid slowing down the communication speed because of the HSI16 startup time. This bit has no effect on HSION value.

0: No effect on HSI16 oscillator.

1: HSI16 oscillator is forced ON even in Stop mode.

#### Bit 8 HSION: HSI16 clock enable

Set and cleared by software.

Cleared by hardware to stop the HSI16 oscillator when entering Stop, Standby or Shutdown mode.

Set by hardware to force the HSI16 oscillator ON when STOPWUCK=1 or HSIASFS = 1 when leaving Stop modes, or in case of failure of the HSE crystal oscillator.

This bit is set by hardware if the HSI16 is used directly or indirectly as system clock.

- 0: HSI16 oscillator OFF

- 1: HSI16 oscillator ON

#### Bits 7:4 **MSIRANGE[3:0]**: MSI clock ranges

These bits are configured by software to choose the frequency range of MSI when MSIRGSEL is set.12 frequency ranges are available:

- 0000: range 0 around 100 kHz

- 0001: range 1 around 200 kHz

- 0010: range 2 around 400 kHz

- 0011: range 3 around 800 kHz

- 0100: range 4 around 1M Hz

- 0101: range 5 around 2 MHz

- 0110: range 6 around 4 MHz (reset value)

- 0111: range 7 around 8 MHz

- 1000: range 8 around 16 MHz

- 1001: range 9 around 24 MHz

- 1010: range 10 around 32 MHz

- 1011: range 11 around 48 MHz

others: not allowed (hardware write protection)

#### Note: Warning: MSIRANGE can be modified when MSI is OFF (MSION=0) or when MSI is ready (MSIRDY=1). MSIRANGE must NOT be modified when MSI is ON and NOT ready (MSION=1 and MSIRDY=0)

#### Bit 3 MSIRGSEL: MSI clock range selection

Set by software to select the MSI clock range with MSIRANGE[3:0]. Write 0 has no effect. After a standby or a reset MSIRGSEL is at 0 and the MSI range value is provided by MSISRANGE in CSR register.

0: MSI Range is provided by MSISRANGE[3:0] in RCC\_CSR register

1: MSI Range is provided by MSIRANGE[3:0] in the RCC\_CR register

#### Bit 2 MSIPLLEN: MSI clock PLL enable

Set and cleared by software to enable/ disable the PLL part of the MSI clock source. MSIPLLEN must be enabled after LSE is enabled (LSEON enabled) and ready (LSERDY set by hardware). There is a hardware protection to avoid enabling MSIPLLEN if LSE is not ready.

This bit is cleared by hardware when LSE is disabled (LSEON = 0) or when the Clock Security System on LSE detects a LSE failure (refer to RCC\_CSR register). 0: MSI PLL OFF 1: MSI PLL ON

#### Bit 1 MSIRDY: MSI clock ready flag

- This bit is set by hardware to indicate that the MSI oscillator is stable.

- 0: MSI oscillator not ready

- 1: MSI oscillator ready

- Note: Once the MSION bit is cleared, MSIRDY goes low after 6 MSI clock cycles.

Bit 0 MSION: MSI clock enable

This bit is set and cleared by software.

Cleared by hardware to stop the MSI oscillator when entering Stop, Standby or Shutdown mode.

Set by hardware to force the MSI oscillator ON when exiting Standby or Shutdown mode. Set by hardware to force the MSI oscillator ON when STOPWUCK=0 when exiting from Stop modes, or in case of a failure of the HSE oscillator

Set by hardware when used directly or indirectly as system clock.

- 0: MSI oscillator OFF

- 1: MSI oscillator ON

# 6.4.2 Internal clock sources calibration register (RCC\_ICSCR)

Address offset: 0x04

Reset value:

0x10XX 00XX where X is factory-programmed (for STM32L475xx/476xx/486xx devices).

0x40XX 00XX where X is factory-programmed (for STM32L496xx/4A6xx devices).

Access: no wait state, word, half-word and byte access

| 31   | 30 | 29 | 28    | 27       | 26   | 25 | 24 | 23 | 22 | 21 | 20   | 19      | 18 | 17 | 16 |

|------|----|----|-------|----------|------|----|----|----|----|----|------|---------|----|----|----|

| Res. |    |    | Н     | SITRIM[6 | 5:0] |    |    |    |    |    | HSIC | AL[7:0] |    |    |    |

|      | rw | rw | rw    | rw       | rw   | rw | rw | r  | r  | r  | r    | r       | r  | r  | r  |

| 15   | 14 | 13 | 12    | 11       | 10   | 9  | 8  | 7  | 6  | 5  | 4    | 3       | 2  | 1  | 0  |

|      |    |    | MSITF | RIM[7:0] |      |    |    |    |    |    | MSIC | AL[7:0] |    |    |    |

| rw   | rw | rw | rw    | rw       | rwr  | rw | rw | r  | r  | r  | r    | r       | r  | r  | r  |

Bit 31 Reserved, must be kept at reset value.

Bits 30:24 HSITRIM[6:0]: HSI16 clock trimming (only HSITRIM[4:0] on STM32L475xx/476xx/486xx devices)

These bits provide an additional user-programmable trimming value that is added to the HSICAL[7:0] bits. It can be programmed to adjust to variations in voltage and temperature that influence the frequency of the HSI16.

The default value is 16 for STM32L475xx/476xx/486xx devices and 64 for STM32L496xx/4A6xx devices; when added to the HSICAL value, the default HSITRIM value will trim the HSI16 to 16 MHz  $\pm$  1 %.

#### Bits 23:16 HSICAL[7:0]: HSI16 clock calibration

These bits are initialized at startup with the factory-programmed HSI16 calibration trim value. When HSITRIM is written, HSICAL is updated with the sum of HSITRIM and the factory trim value.

#### Bits 15:8 MSITRIM[7:0]: MSI clock trimming

These bits provide an additional user-programmable trimming value that is added to the MSICAL[7:0] bits. It can be programmed to adjust to variations in voltage and temperature that influence the frequency of the MSI.

#### Bits 7:0 MSICAL[7:0]: MSI clock calibration

These bits are initialized at startup with the factory-programmed MSI calibration trim value. When MSITRIM is written, MSICAL is updated with the sum of MSITRIM and the factory trim value.

# 6.4.3 Clock configuration register (RCC\_CFGR)

Address offset: 0x08

Reset value: 0x0000 0000

Access:  $0 \le$  wait state  $\le 2$ , word, half-word and byte access

1 or 2 wait states inserted only if the access occurs during clock source switch.

From 0 to 15 wait states inserted if the access occurs when the APB or AHB prescalers values update is on going.

| 31           | 30   | 29      | 28       | 27 | 26   | 25       | 24 | 23   | 22   | 21    | 20   | 19   | 18     | 17   | 16    |

|--------------|------|---------|----------|----|------|----------|----|------|------|-------|------|------|--------|------|-------|

| Res.         | M    | COPRE[2 | ::0]     |    | MCOS | SEL[3:0] |    | Res. | Res. | Res.  | Res. | Res. | Res.   | Res. | Res.  |

|              | rw   | rw      | rw       | rw | rw   | rw       | rw |      |      |       |      |      |        |      |       |

| 15           | 14   | 13      | 12       | 11 | 10   | 9        | 8  | 7    | 6    | 5     | 4    | 3    | 2      | 1    | 0     |

| STOP<br>WUCK | Res. | Р       | PRE2[2:0 | )] | F    | PRE1[2:0 | 0] |      | HPRE | [3:0] |      | SWS  | 6[1:0] | SW   | [1:0] |

| rw           |      | rw      | rw       | rw | rw   | rw       | rw | rw   | rw   | rw    | rw   | r    | r      | rw   | rw    |

Bit 31 Reserved, must be kept at reset value.

Bits 30:28 MCOPRE[2:0]: Microcontroller clock output prescaler

These bits are set and cleared by software.

It is highly recommended to change this prescaler before MCO output is enabled.

000: MCO is divided by 1

- 001: MCO is divided by 2

- 010: MCO is divided by 4

- 011: MCO is divided by 8

- 100: MCO is divided by 16

Others: not allowed

Bits 27:24 MCOSEL[3:0]: Microcontroller clock output (MCOSEL[2:0] only for

STM32L475xx/476xx/486xx devices)

Set and cleared by software.

0000: MCO output disabled, no clock on MCO

0001: SYSCLK system clock selected

- 0010: MSI clock selected.

- 0011: HSI16 clock selected.

- 0100: HSE clock selected

- 0101: Main PLL clock selected

- 0110: LSI clock selected

- 0111: LSE clock selected

1000: Internal HSI48 clock selected (only for STM32L496xx/4A6xx devices)

Others: Reserved

Note: This clock output may have some truncated cycles at startup or during MCO clock source switching.

Bits 23:16 Reserved, must be kept at reset value.

Bit 15 STOPWUCK: Wakeup from Stop and CSS backup clock selection

Set and cleared by software to select the system clock used when exiting Stop mode. The selected clock is also used as emergency clock for the Clock Security System on HSE. Warning: STOPWUCK must not be modified when the Clock Security System is enabled by HSECSSON in RCC\_CR register and the system clock is HSE (SWS="10") or a switch on HSE is requested (SW="10").

0: MSI oscillator selected as wakeup from stop clock and CSS backup clock.

1: HSI16 oscillator selected as wakeup from stop clock and CSS backup clock

Bit 14 Reserved, must be kept at reset value.

#### Bits 13:11 PPRE2[2:0]: APB high-speed prescaler (APB2)

Set and cleared by software to control the division factor of the APB2 clock (PCLK2).

- 0xx: HCLK not divided

- 100: HCLK divided by 2

- 101: HCLK divided by 4

- 110: HCLK divided by 8

- 111: HCLK divided by 16

Bits 10:8 **PPRE1[2:0]:**APB low-speed prescaler (APB1)

Set and cleared by software to control the division factor of the APB1 clock (PCLK1).

- 0xx: HCLK not divided

- 100: HCLK divided by 2

- 101: HCLK divided by 4 110: HCLK divided by 8

- 111: HCLK divided by 16

- Bits 7:4 HPRE[3:0]: AHB prescaler

Set and cleared by software to control the division factor of the AHB clock.

- **Caution:** Depending on the device voltage range, the software has to set correctly these bits to ensure that the system frequency does not exceed the maximum allowed frequency (for more details please refer to *Section 5.1.8: Dynamic voltage scaling management*). After a write operation to these bits and before decreasing the voltage range, this register must be read to be sure that the new value has been taken into account.

- 0xxx: SYSCLK not divided

- 1000: SYSCLK divided by 2

- 1001: SYSCLK divided by 4

- 1010: SYSCLK divided by 8

- 1011: SYSCLK divided by 16

- 1100: SYSCLK divided by 64

- 1101: SYSCLK divided by 128

- 1110: SYSCLK divided by 256

- 1111: SYSCLK divided by 512

- Bits 3:2 SWS[1:0]: System clock switch status

- Set and cleared by hardware to indicate which clock source is used as system clock.

- 00: MSI oscillator used as system clock

- 01: HSI16 oscillator used as system clock

- 10: HSE used as system clock

- 11: PLL used as system clock

Bits 1:0 SW[1:0]: System clock switch

Set and cleared by software to select system clock source (SYSCLK).

Configured by HW to force MSI oscillator selection when exiting Standby or Shutdown mode. Configured by HW to force MSI or HSI16 oscillator selection when exiting Stop mode or in case of failure of the HSE oscillator, depending on STOPWUCK value.

00: MSI selected as system clock

01: HSI16 selected as system clock

10: HSE selected as system clock

11: PLL selected as system clock

# 6.4.4 PLL configuration register (RCC\_PLLCFGR)

Address offset: 0x0C

Reset value: 0x0000 1000

Access: no wait state, word, half-word and byte access

This register is used to configure the PLL clock outputs according to the formulas:

• f(VCO clock) = f(PLL clock input) × (PLLN / PLLM)

- f(PLL\_P) = f(VCO clock) / PLLP

- f(PLL\_Q) = f(VCO clock) / PLLQ

- f(PLL\_R) = f(VCO clock) / PLLR

| 31   | 30 | 29       | 28  | 27       | 26   | 25     | 24         | 23   | 22   | 21       | 20         | 19   | 18   | 17    | 16         |

|------|----|----------|-----|----------|------|--------|------------|------|------|----------|------------|------|------|-------|------------|

|      | PL | LPDIV[4: | :0] |          | PLLF | R[1:0] | PLL<br>REN | Res. | PLLC | ג[1:0]   | PLL<br>QEN | Res. | Res. | PLLP  | PLL<br>PEN |

| rw   | rw | rw       | rw  | rw       | rw   | rw     | rw         |      | rw   | rw       | rw         |      |      | rw    | rw         |

| 15   | 14 | 13       | 12  | 11       | 10   | 9      | 8          | 7    | 6    | 5        | 4          | 3    | 2    | 1     | 0          |

| Res. |    |          |     | PLLN[7:0 | 0]   |        |            | Res. | I    | PLLM[2:0 | ]          | Res. | Res. | PLLSF | RC[1:0]    |

|      | rw | rw       | rw  | rw       | rw   | rw     | rw         |      | rw   | rw       | rw         |      |      | rw    | rw         |

Bits 31:27 **PLLPDIV[4:0]**: Main PLL division factor for PLLSAI2CLK (only for STM32L496xx/4A6xx devices)

Set and cleared by software to control the SAI1 or SAI2 clock frequency. PLLSAI3CLK output clock frequency = VCO frequency / PLLPDIV. 00000: PLLSAI3CLK is controlled by the bit PLLP 00001: Reserved. 00010: PLLSAI3CLK = VCO / 2

11111: PLLSAI3CLK = VCO / 31

Bits 26:25 PLLR[1:0]: Main PLL division factor for PLLCLK (system clock)

Set and cleared by software to control the frequency of the main PLL output clock PLLCLK. This output can be selected as system clock. These bits can be written only if PLL is disabled.

PLLCLK output clock frequency = VCO frequency / PLLR with PLLR = 2, 4, 6, or 8

00: PLLR = 2

01: PLLR = 4

10: PLLR = 6

11: PLLR = 8

- **Caution:** The software has to set these bits correctly not to exceed 80 MHz on this domain.

- Bit 24 PLLREN: Main PLL PLLCLK output enable

Set and reset by software to enable the PLLCLK output of the main PLL (used as system clock).

This bit cannot be written when PLLCLK output of the PLL is used as System Clock. In order to save power, when the PLLCLK output of the PLL is not used, the value of PLLREN should be 0.

- 0: PLLCLK output disable

- 1: PLLCLK output enable

Bit 23 Reserved, must be kept at reset value.

Bits 22:21 PLLQ[1:0]: Main PLL division factor for PLL48M1CLK (48 MHz clock).

Set and cleared by software to control the frequency of the main PLL output clock PLL48M1CLK. This output can be selected for USB, RNG, SDMMC (48 MHz clock). These bits can be written only if PLL is disabled.

PLL48M1CLK output clock frequency = VCO frequency / PLLQ with PLLQ = 2, 4, 6, or 8 00: PLLQ = 2

- 01: PLLQ = 4

- 10: PLLQ = 6

- 11: PLLQ = 8

- **Caution:** The software has to set these bits correctly not to exceed 80 MHz on this domain.

- Bit 20 PLLQEN: Main PLL PLL48M1CLK output enable

Set and reset by software to enable the PLL48M1CLK output of the main PLL. In order to save power, when the PLL48M1CLK output of the PLL is not used, the value of PLLQEN should be 0.

0: PLL48M1CLK output disable

1: PLL48M1CLK output enable

- Bits 19:18 Reserved, must be kept at reset value.

- Bit 17 PLLP: Main PLL division factor for PLLSAI3CLK (SAI1 and SAI2 clock).

Set and cleared by software to control the frequency of the main PLL output clock PLLSAI3CLK. This output can be selected for SAI1 or SAI2. These bits can be written only if PLL is disabled. (When the PLLPDIVI4:0] is set to "00000" only for STM32L496xx/4A6xx

devices)PLLSAI3CLK output clock frequency = VCO frequency / PLLP with PLLP =7, or 17 0: PLLP = 7

1: PLLP = 17

**Caution:** The software has to set these bits correctly not to exceed 80 MHz on this domain.

Bit 16 **PLLPEN**: Main PLL PLLSAI3CLK output enable

Set and reset by software to enable the PLLSAI3CLK output of the main PLL. In order to save power, when the PLLSAI3CLK output of the PLL is not used, the value of PLLPEN should be 0. 0: PLLSAI3CLK output disable

- 1: PLLSAI3CLK output enable

- Bit 15 Reserved, must be kept at reset value.

- Bits 14:8 PLLN[6:0]: Main PLL multiplication factor for VCO

```

Set and cleared by software to control the multiplication factor of the VCO. These bits can be

written only when the PLL is disabled.

VCO output frequency = VCO input frequency x PLLN with 8 =< PLLN =< 86

0000000: PLLN = 0 wrong configuration

0000001: PLLN = 1 wrong configuration

...

0000111: PLLN = 7 wrong configuration

0001000: PLLN = 8

0001001: PLLN = 8

0001001: PLLN = 8

1010101: PLLN = 85

1010110: PLLN = 85

1010111: PLLN = 87 wrong configuration

...

1111111: PLLN = 127 wrong configuration

```

- **Caution:** The software has to set correctly these bits to assure that the VCO output frequency is between 64 and 344 MHz.

- Bit 7 Reserved, must be kept at reset value.

- Bits 6:4 PLLM: Division factor for the main PLL and audio PLL (PLLSAI1 and PLLSAI2) input clock

Set and cleared by software to divide the PLL, PLLSAI1 and PLLSAI2 input clock before the VCO. These bits can be written only when all PLLs are disabled. VCO input frequency = PLL input clock frequency / PLLM with 1 <= PLLM <= 8 000: PLLM = 1 001: PLLM = 2 010: PLLM = 2 010: PLLM = 3 011: PLLM = 4 100: PLLM = 5 101: PLLM = 6 110: PLLM = 7 111: PLLM = 8

**Caution:** The software has to set these bits correctly to ensure that the VCO input frequency ranges from 4 to 16 MHz.

Bits 3:2 Reserved, must be kept at reset value.

Bits 1:0 PLLSRC: Main PLL, PLLSAI1 and PLLSAI2 entry clock source

Set and cleared by software to select PLL, PLLSAI1 and PLLSAI2 clock source. These bits can be written only when PLL, PLLSAI1 and PLLSAI2 are disabled. In order to save power, when no PLL is used, the value of PLLSRC should be 00. 00: No clock sent to PLL, PLLSAI1 and PLLSAI2

01: MSI clock selected as PLL, PLLSAI1 and PLLSAI2 clock entry

10: HSI16 clock selected as PLL, PLLSAI1 and PLLSAI2 clock entry

11: HSE clock selected as PLL, PLLSAI1 and PLLSAI2 clock entry

# 6.4.5 PLLSAI1 configuration register (RCC\_PLLSAI1CFGR)

Address offset: 0x10

Reset value: 0x0000 1000

Access: no wait state, word, half-word and byte access

This register is used to configure the PLLSAI1 clock outputs according to the formulas:

- f(VCOSAI1 clock) = f(PLL clock input) × (PLLSAI1N / PLLM)

- f(PLLSAI1\_P) = f(VCOSAI1 clock) / PLLSAI1P

- f(PLLSAI1\_Q) = f(VCOSAI1 clock) / PLLSAI1Q

- f(PLLSAI1\_R) = f(VCOSAI1 clock) / PLLSAI1R

| 31   | 30   | 29       | 28             | 27     | 26    | 25       | 24                 | 23   | 22    | 21       | 20                 | 19   | 18   | 17           | 16                 |

|------|------|----------|----------------|--------|-------|----------|--------------------|------|-------|----------|--------------------|------|------|--------------|--------------------|

|      | PLLS | Sai1PDIV | <b>/</b> [4:0] |        | PLLSA | I1R[1:0] | PLL<br>SAI1<br>REN | Res. | PLLSA | I1Q[1:0] | PLL<br>SAI1<br>QEN | Res. | Res. | PLL<br>SAI1P | PLL<br>SAI1<br>PEN |

| rw   | rw   | rw       | rw             | rw     | rw    | rw       | rw                 |      | rw    | rw       | rw                 |      |      | rw           | rw                 |

| 15   | 14   | 13       | 12             | 11     | 10    | 9        | 8                  | 7    | 6     | 5        | 4                  | 3    | 2    | 1            | 0                  |

| Res. |      |          | PL             | LSAI1N | [6:0] |          |                    | Res. | Res.  | Res.     | Res.               | Res. | Res. | Res.         | Res.               |

|      | rw   | rw       | rw             | rw     | rw    | rw       | rw                 |      |       |          |                    |      |      |              |                    |

Bits 31:27 **PLLSAI1PDIV[4:0]**: PLLSAI1 division factor for PLLSAI1CLK (only on STM32L496xx/4A6xx devices)

Set and cleared by software to control the SAI1 or SAI2 clock frequency. PLLSAI1CLK output clock frequency = VCOSAI1 frequency / PLLPDIV.

00000: PLLSAI1CLK is controlled by the bit PLLP

00001: Reserved.

00010: PLLSAI1CLK = VCOSAI1 / 2

....

11111: PLLSAI1CLK = VCOSAI1 / 31

Bits 26:25 PLLSAI1R[1:0]: PLLSAI1 division factor for PLLADC1CLK (ADC clock)

Set and cleared by software to control the frequency of the PLLSAI1 output clock PLLADC1CLK. This output can be selected as ADC clock. These bits can be written only if PLLSAI1 is disabled.

PLLADC1CLK output clock frequency = VCOSAI1 frequency / PLLSAI1R with PLLSAI1R = 2, 4, 6, or 8

- 00: PLLSAI1R = 2

- 01: PLLSAI1R = 4

- 10: PLLSAI1R = 6

- 11: PLLSAI1R = 8

#### Bit 24 PLLSAI1REN: PLLSAI1 PLLADC1CLK output enable

Set and reset by software to enable the PLLADC1CLK output of the PLLSAI1 (used as clock for ADC).

In order to save power, when the PLLADC1CLK output of the PLLSAI1 is not used, the value of PLLSAI1REN should be 0.

- 0: PLLADC1CLK output disable

- 1: PLLADC1CLK output enable

- Bit 23 Reserved, must be kept at reset value.

- Bits 22:21 PLLSAI1Q[1:0]: PLLSAI1 division factor for PLL48M2CLK (48 MHz clock)

Set and cleared by software to control the frequency of the PLLSAI1 output clock PLL48M2CLK. This output can be selected for USB, RNG, SDMMC (48 MHz clock). These bits can be written only if PLLSAI1 is disabled.

PLL48M2CLK output clock frequency = VCOSAI1 frequency / PLLQ with PLLQ = 2, 4, 6, or 8

- 00: PLLQ = 2

- 01: PLLQ = 4

- 10: PLLQ = 6

- 11: PLLQ = 8

- **Caution:** The software has to set these bits correctly not to exceed 80 MHz on this domain.

- Bit 20 PLLSAI1QEN: PLLSAI1 PLL48M2CLK output enable

Set and reset by software to enable the PLL48M2CLK output of the PLLSAI1.

In order to save power, when the PLL48M2CLK output of the PLLSAI1 is not used, the value of PLLSAI1QEN should be 0.

- 0: PLL48M2CLK output disable

- 1: PLL48M2CLK output enable

Bits 19:18 Reserved, must be kept at reset value.

```

Bit 17 PLLSAI1P: PLLSAI1 division factor for PLLSAI1CLK (SAI1 or SAI2 clock).

Set and cleared by software to control the frequency of the PLLSAI1 output clock

PLLSAI1CLK. This output can be selected for SAI1 or SAI2. These bits can be written only if

PLLSAI1 is disabled.

(When the PLLSAI1PDIV[4:0] is set to "00000" only on STM32L496xx/4A6xx

devices), PLLSAI1CLK output clock frequency = VCOSAI1 frequency / PLLSAI1P with

PLLSAI1P =7, or 17

0: PLLSAI1P = 7

1: PLLSAI1P = 17

Bit 16 PLLSAI1PEN: PLLSAI1 PLLSAI1CLK output enable

Set and reset by software to enable the PLLSAI1CLK output of the PLLSAI1.

In order to save power, when the PLLSAI1CLK output of the PLLSAI1 is not used, the value

of PLLSAI1PEN should be 0.

0: PLLSAI1CLK output disable

1: PLLSAI1CLK output enable

Bit 15 Reserved, must be kept at reset value.

Bits 14:8 PLLSAI1N[6:0]: PLLSAI1 multiplication factor for VCO

Set and cleared by software to control the multiplication factor of the VCO. These bits can be

written only when the PLLSAI1 is disabled.

VCOSAI1 output frequency = VCOSAI1 input frequency x PLLSAI1N

with 8 =< PLLSAI1N =< 86

0000000: PLLSAI1N = 0 wrong configuration

0000001: PLLSAI1N = 1 wrong configuration

0000111: PLLSAI1N = 7 wrong configuration

0001000: PLLSAI1N = 8

0001001: PLLSAI1N = 9

...

1010101: PLLSAI1N = 85

1010110: PLLSAI1N = 86

1010111: PLLSAI1N = 87 wrong configuration

1111111: PLLSAI1N = 127 wrong configuration

```

**Caution:** The software has to set correctly these bits to ensure that the VCO output frequency is between 64 and 344 MHz.

Bits 7:0 Reserved, must be kept at reset value.

#### RM0351

# 6.4.6 PLLSAI2 configuration register (RCC\_PLLSAI2CFGR)

Address offset: 0x14

Reset value: 0x0000 1000

Access: no wait state, word, half-word and byte access

This register is used to configure the PLLSAI2 clock outputs according to the formulas:

- f(VCOSAI2 clock) = f(PLL clock input) × (PLLSAI2N / PLLM)

- f(PLLSAI2\_P) = f(VCOSAI2 clock) / PLLSAI2P

- f(PLLSAI2\_R) = f(VCOSAI2 clock) / PLLSAI2R

| 31   | 30   | 29      | 28    | 27      | 26    | 25       | 24                 | 23   | 22   | 21        | 20                 | 19   | 18   | 17           | 16                 |

|------|------|---------|-------|---------|-------|----------|--------------------|------|------|-----------|--------------------|------|------|--------------|--------------------|

|      | PLLS | ai2pdiv | [4:0] |         | PLLSA | I2R[1:0] | PLL<br>SAI2<br>REN | Res. |      | LL<br>I2Q | PLL<br>SAI2<br>QEN | Res. | Res. | PLL<br>SAI2P | PLL<br>SAI2<br>PEN |

| rw   | rw   | rw      | rw    | rw      | rw    | rw       | rw                 |      |      |           |                    |      |      | rw           | rw                 |

| 15   | 14   | 13      | 12    | 11      | 10    | 9        | 8                  | 7    | 6    | 5         | 4                  | 3    | 2    | 1            | 0                  |

| Res. |      |         | PL    | LSAI2N[ | 6:0]  |          |                    | Res. | Res. | Res.      | Res.               | Res. | Res. | Res.         | Res.               |

|      | rw   | rw      | rw    | rw      | rw    | rw       | rw                 |      |      |           |                    |      |      |              |                    |

Bits 31:27 **PLLSAI2PDIV[4:0]**: PLLSAI2 division factor for PLLSAI2CLK (only on STM32L496xx/4A6xx devices)

Set and cleared by software to control the SAI1 or SAI2 clock frequency. PLLSAI2CLK output clock

frequency = VCOSAI2 frequency / PLLSAI2PDIV.

00000: PLLSAI2CLK is controlled by the bit PLLSAI2P

00001: Reserved.

00010: PLLSAI2CLK = VCOSAI2 / 2

11111: PLLSAI2CLK = VCOSAI2 / 31

Bits 26:25 **PLLSAI2R[1:0]**: PLLSAI2 division factor for PLLADC2CLK (ADC clock)

Set and cleared by software to control the frequency of the PLLSAI2 output clock PLLADC2CLK. This output can be selected as ADC clock. These bits can be written only if PLLSAI2 is disabled.

PLLADC2CLK output clock frequency = VCOSAI2 frequency / PLLSAI2R with PLLSAI2R = 2, 4, 6, or 8

- 00: PLLSAI2R = 2

- 01: PLLSAI2R = 4

- 10: PLLSAI2R = 6

- 11: PLLSAI2R = 8

#### Bit 24 PLLSAI2REN: PLLSAI2 PLLADC2CLK output enable

Set and reset by software to enable the PLLADC2CLK output of the PLLSAI2 (used as clock for ADC).

In order to save power, when the PLLADC2CLK output of the PLLSAI2 is not used, the value of PLLSAI2REN should be 0.

- 0: PLLADC2CLK output disable

- 1: PLLADC2CLK output enable

Bits 23:18 Reserved, must be kept at reset value.

Bit 17 PLLSAI2P: PLLSAI2 division factor for PLLSAI2CLK (SAI1 or SAI2 clock).

Set and cleared by software to control the frequency of the PLLSAI2 output clock PLLSAI2CLK. This output can be selected for SAI1 or SAI2. These bits can be written only if PLLSAI2 is disabled.

(when the PLLSAI2PDIV[4:0] is set to "00000" on STM32L496xx/4A6xx devices), PLLSAI2CLK output clock frequency = VCOSAI2 frequency / PLLSAI2P with PLLSAI2P =7, or 17 0: PLLSAI2P = 7

1: PLLSAI2P = 17

Bit 16 PLLSAI2PEN: PLLSAI2 PLLSAI2CLK output enable

Set and reset by software to enable the PLLSAI2CLK output of the PLLSAI2. In order to save power, when the PLLSAI2CLK output of the PLLSAI2 is not used, the value of PLLSAI2PEN should be 0. 0: PLLSAI2CLK output disable

1: PLLSAI2CLK output enable

Bit 15 Reserved, must be kept at reset value.

Bits 14:8 PLLSAI2N[6:0]: PLLSAI2 multiplication factor for VCO

Set and cleared by software to control the multiplication factor of the VCO. These bits can be written only when the PLLSAI2 is disabled.

VCOSAI2 output frequency = VCOSAI2 input frequency x PLLSAI2N

with 8 =< PLLSAI2N =< 86</li>

0000000: PLLSAI2N = 0 wrong configuration

0000001: PLLSAI2N = 1 wrong configuration

...

0000111: PLLSAI2N = 7 wrong configuration

0001000: PLLSAI2N = 8

0001001: PLLSAI2N = 9

1010101: PLLSAI2N = 85 1010110: PLLSAI2N = 86 1010111: PLLSAI2N = 87 wrong configuration

1111111: PLLSAI2N = 127 wrong configuration

**Caution:** The software has to set correctly these bits to ensure that the VCO output frequency is between 64 and 344 MHz.

Bits 7:0 Reserved, must be kept at reset value.

# 6.4.7 Clock interrupt enable register (RCC\_CIER)

Address offset: 0x18

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

| 31   | 30   | 29   | 28   | 27   | 26             | 25           | 24   | 23                   | 22                   | 21           | 20           | 19           | 18           | 17           | 16           |

|------|------|------|------|------|----------------|--------------|------|----------------------|----------------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Res. | Res. | Res. | Res. | Res. | Res.           | Res.         | Res. | Res.                 | Res.                 | Res.         | Res.         | Res.         | Res.         | Res.         | Res.         |

|      |      |      |      |      |                |              |      |                      |                      |              |              |              |              |              |              |

| 15   | 14   | 13   | 12   | 11   | 10             | 9            | 8    | 7                    | 6                    | 5            | 4            | 3            | 2            | 1            | 0            |

| Res. | Res. | Res. | Res. | Res. | HSI48<br>RDYIE | LSE<br>CSSIE | Res. | PLL<br>SAI2<br>RDYIE | PLL<br>SAI1<br>RDYIE | PLL<br>RDYIE | HSE<br>RDYIE | HSI<br>RDYIE | MSI<br>RDYIE | LSE<br>RDYIE | LSI<br>RDYIE |

|      |      |      |      |      | rw             | rw           |      | rw                   | rw                   | rw           | rw           | rw           | rw           | rw           | rw           |

Bits 31:11 Reserved, must be kept at reset value.

Bit 10 HSI48RDYIE: HSI48 ready interrupt enable (only on STM32L496xx/4A6xx devices)

Set and cleared by software to enable/disable interrupt caused by the internal HSI48 oscillator.

- 0: HSI48 ready interrupt disabled

- 1: HSI48 ready interrupt enabled

#### Bit 9 **LSECSSIE**: LSE clock security system interrupt enable

Set and cleared by software to enable/disable interrupt caused by the clock security system on LSE.

- 0: Clock security interrupt caused by LSE clock failure disabled

- 1: Clock security interrupt caused by LSE clock failure enabled

- Bit 8 Reserved, must be kept at reset value.

#### Bit 7 PLLSAI2RDYIE: PLLSAI2 ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by PLLSAI2 lock.

- 0: PLLSAI2 lock interrupt disabled

- 1: PLLSAI2 lock interrupt enabled

#### Bit 6 PLLSAI1RDYIE: PLLSAI1 ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by PLSAI1L lock. 0: PLLSAI1 lock interrupt disabled 1: PLLSAI1 lock interrupt enabled

#### Bit 5 **PLLRDYIE**: PLL ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by PLL lock.

- 0: PLL lock interrupt disabled

- 1: PLL lock interrupt enabled

#### Bit 4 HSERDYIE: HSE ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the HSE oscillator stabilization.

- 0: HSE ready interrupt disabled

- 1: HSE ready interrupt enabled

#### Bit 3 HSIRDYIE: HSI16 ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the HSI16 oscillator stabilization.

- 0: HSI16 ready interrupt disabled

- 1: HSI16 ready interrupt enabled

#### Bit 2 MSIRDYIE: MSI ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the MSI oscillator stabilization.

0: MSI ready interrupt disabled

1: MSI ready interrupt enabled

#### Bit 1 LSERDYIE: LSE ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the LSE oscillator stabilization.

0: LSE ready interrupt disabled

- 1: LSE ready interrupt enabled

- Bit 0 LSIRDYIE: LSI ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the LSI oscillator stabilization.

0: LSI ready interrupt disabled

1: LSI ready interrupt enabled

# 6.4.8 Clock interrupt flag register (RCC\_CIFR)

Address offset: 0x1C

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

| 31   | 30   | 29   | 28   | 27   | 26            | 25          | 24   | 23   | 22              | 21          | 20          | 19          | 18          | 17          | 16          |

|------|------|------|------|------|---------------|-------------|------|------|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Res. | Res. | Res. | Res. | Res. | Res.          | Res.        | Res. | Res. | Res.            | Res.        | Res.        | Res.        | Res.        | Res.        | Res.        |

|      |      |      |      |      |               |             |      |      |                 |             |             |             |             |             |             |

| 15   | 14   | 13   | 12   | 11   | 10            | 9           | 8    | 7    | 6               | 5           | 4           | 3           | 2           | 1           | 0           |

| Res. | Res. | Res. | Res. | Res. | HSI48<br>RDYF | LSE<br>CSSF | CSSF |      | PLLSAI<br>1RDYF | PLL<br>RDYF | HSE<br>RDYF | HSI<br>RDYF | MSI<br>RDYF | LSE<br>RDYF | LSI<br>RDYF |

|      |      |      |      |      |               | r           | r    | r    | r               | r           | r           | r           | r           | r           | r           |

Bits 31:11 Reserved, must be kept at reset value.

Bit 10 HSI48RDYF: HSI48 ready interrupt flag (only on STM32L496xx/4A6xx devices) Set by hardware when the HSI48 clock becomes stable and HSI48RDYIE is set in a response to setting the HSI48ON (refer to *Clock recovery RC register (RCC\_CRRCR)*). Cleared by software setting the HSI48RDYC bit.

- 0: No clock ready interrupt caused by the HSI48 oscillator

- 1: Clock ready interrupt caused by the HSI48 oscillator