# Cortex<sup>®</sup>-M3

**Revision r2p0**

**Technical Reference Manual**

Copyright © 2005-2008, 2010 ARM Limited. All rights reserved. ARM DDI 0337H (ID032710)

# Cortex-M3 Technical Reference Manual

Copyright © 2005-2008, 2010 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

Change History

| Date              | Issue | Confidentiality  | Change                                 |

|-------------------|-------|------------------|----------------------------------------|

| 15 December 2005  | А     | Confidential     | First Release                          |

| 13 January 2006   | В     | Non-Confidential | Confidentiality status amended         |

| 10 May 2006       | С     | Non-Confidential | First Release for r1p0                 |

| 27 September 2006 | D     | Non-Confidential | First Release for r1p1                 |

| 13 June 2007      | Е     | Non-Confidential | Minor update with no technical changes |

| 11 April 2008     | F     | Confidential     | Limited release for SC300 r0p0         |

| 26 June 2008      | G     | Non-Confidential | First Release for r2p0                 |

| 26 February 2010  | Н     | Non-Confidential | Second Release for r2p0                |

#### **Proprietary Notice**

Words and logos marked with \* or \* are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM Limited in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is Final (information on a developed product).

#### Web Address

http://www.arm.com

# Contents Cortex-M3 Technical Reference Manual

|           | Pref  | ace                              |      |

|-----------|-------|----------------------------------|------|

|           |       | About this book                  | x    |

|           |       | Feedback                         | xiii |

| Chapter 1 | Intro | oduction                         |      |

| -         | 1.1   | About the processor              |      |

|           | 1.2   | Features                         |      |

|           | 1.3   | Interfaces                       |      |

|           | 1.4   | Configurable options             |      |

|           | 1.5   | Product documentation            |      |

|           | 1.6   | Product revisions                | 1-9  |

| Chapter 2 | Fund  | ctional Description              |      |

| -         | 2.1   | About the functions              |      |

|           | 2.2   | Interfaces                       | 2-4  |

| Chapter 3 | Prog  | grammers Model                   |      |

| -         | 3.1   | About the programmers model      |      |

|           | 3.2   | Modes of operation and execution |      |

|           | 3.3   | Instruction set summary          |      |

|           | 3.4   | System address map               |      |

|           | 3.5   | Write buffer                     |      |

|           | 3.6   | Exclusive monitor                |      |

|           | 3.7   | Bit-banding                      |      |

|           | 3.8   | Processor core register summary  |      |

|           | 3.9   | Exceptions                       |      |

| Chapter 4  | Syste | em Control                                      |      |

|------------|-------|-------------------------------------------------|------|

| •          | 4.1   | About system control                            | 4-2  |

|            | 4.2   | Register summary                                | 4-3  |

|            | 4.3   | Register descriptions                           | 4-5  |

| Chapter 5  | Mem   | ory Protection Unit                             |      |

| -          | 5.1   | About the MPU                                   | 5-2  |

|            | 5.2   | MPU functional description                      |      |

|            | 5.3   | MPU programmers model                           | 5-4  |

| Chapter 6  | Nest  | ed Vectored Interrupt Controller                |      |

| -          | 6.1   | About the NVIC                                  |      |

|            | 6.2   | NVIC functional description                     | 6-3  |

|            | 6.3   | NVIC programmers model                          |      |

| Chapter 7  | Debu  | Ig                                              |      |

| •          | 7.1   | About debug                                     |      |

|            | 7.2   | About the AHB-AP                                |      |

|            | 7.3   | About the Flash Patch and Breakpoint Unit (FPB) |      |

| Chapter 8  | Data  | Watchpoint and Trace Unit                       |      |

| -          | 8.1   | About the DWT                                   |      |

|            | 8.2   | DWT functional description                      | 8-3  |

|            | 8.3   | DWT Programmers Model                           |      |

| Chapter 9  | Instr | umentation Trace Macrocell Unit                 |      |

| •          | 9.1   | About the ITM                                   |      |

|            | 9.2   | ITM functional description                      |      |

|            | 9.3   | ITM programmers model                           |      |

| Chapter 10 | Emb   | edded Trace Macrocell                           |      |

| -          | 10.1  | About the ETM                                   | 10-2 |

|            | 10.2  | ETM functional description                      | 10-3 |

|            | 10.3  | ETM Programmers model                           | 10-9 |

| Chapter 11 | Trace | e Port Interface Unit                           |      |

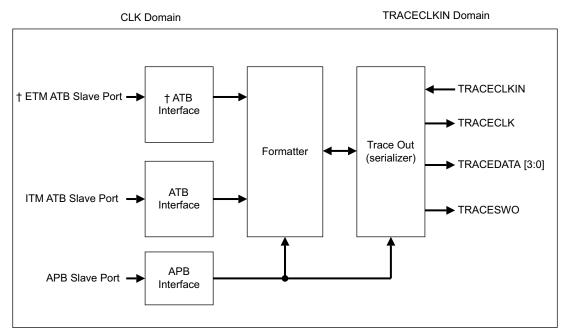

|            | 11.1  | About the Cortex-M3 TPIU                        | 11-2 |

|            | 11.2  | TPIU functional description                     | 11-3 |

|            | 11.3  | TPIU programmers model                          | 11-5 |

| Appendix A | Revis | sions                                           |      |

|            | Glos  | sary                                            |      |

# List of Tables Cortex-M3 Technical Reference Manual

|             | Change History                            | ii    |

|-------------|-------------------------------------------|-------|

| Table 3-1   | Cortex-M3 instruction set summary         |       |

| Table 3-2   | Memory regions                            |       |

| Table 4-1   | System control registers                  |       |

| Table 4-2   | ACTLR bit assignments                     |       |

| Table 4-3   | CPUID bit assignments                     |       |

| Table 4-4   | AFSR bit assignments                      |       |

| Table 5-1   | MPU registers                             |       |

| Table 6-1   | NVIC registers                            |       |

| Table 6-2   | ICTR bit assignments                      |       |

| Table 7-1   | Cortex-M3 ROM table identification values |       |

| Table 7-2   | Cortex-M3 ROM table components            |       |

| Table 7-3   | SCS identification values                 |       |

| Table 7-4   | Debug registers                           |       |

| Table 7-5   | AHB-AP register summary                   |       |

| Table 7-6   | CSW bit assignments                       |       |

| Table 7-7   | FPB register summary                      |       |

| Table 8-1   | DWT register summary                      |       |

| Table 9-1   | ITM register summary                      |       |

| Table 9-2   | ITM_TPR bit assignments                   |       |

| Table 10-1  | Cortex-M3 resources                       | 10-4  |

| Table 10-2  | Boolean function encoding for events      | 10-5  |

| Table 10-3  | Resource identification encoding          | 10-5  |

| Table 10-4  | Input connections                         | 10-7  |

| Table 10-5  | Trigger output connections                | 10-7  |

| Table 10-6  | ETM registers                             |       |

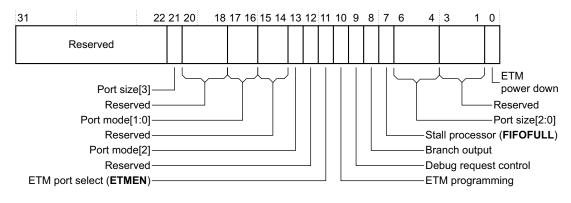

| Table 10-7  | ETMCR bit assignments                     | 10-11 |

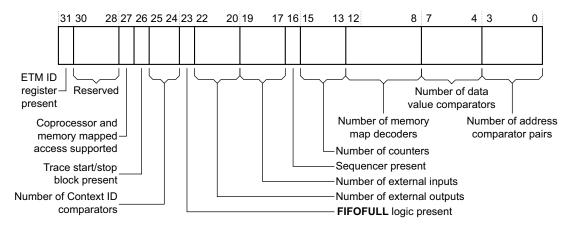

| Table 10-8  | ETMCCR bit assignments                    | 10-13 |

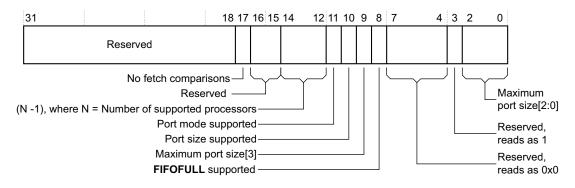

| Table 10-9  | ETMSCR bit assignments                    |       |

| Table 10-10 | ETMTECR1 bit assignments                  | 10-15 |

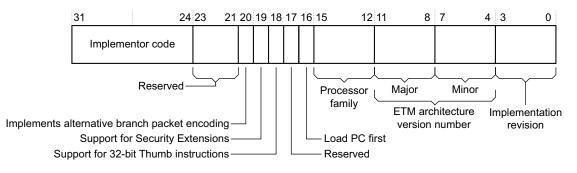

| Table 10-11 | ETMIDR bit assignments                  | 10-16  |

|-------------|-----------------------------------------|--------|

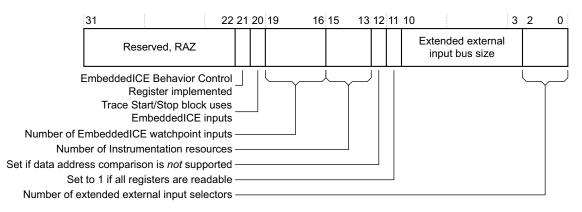

| Table 10-12 | ETMCCER bit assignments                 |        |

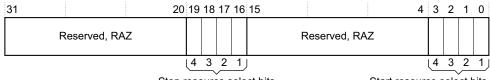

| Table 10-13 | ETMTESSEICR bit assignments             |        |

| Table 10-14 | ETMPDSR bit assignments                 | 10-19  |

| Table 10-15 | ITMISCIN bit assignments                | 10-19  |

| Table 10-16 | ITTRIGOUT bit assignments               |        |

| Table 10-17 | ETM_ITATBCTR2 bit assignments           | 10-21  |

| Table 10-18 | ETM_ITATBCTR0 bit assignments           | 10-21  |

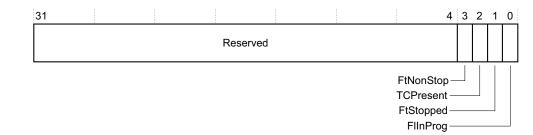

| Table 11-1  | TPIU registers                          | . 11-5 |

| Table 11-2  | TPIU_ACPR bit assignments               | . 11-6 |

| Table 11-3  | TPIU_FFSR bit assignments               | . 11-7 |

| Table 11-4  | TPIU_FFCR bit assignments               | . 11-7 |

| Table 11-5  | TRIGGER bit assignments                 | . 11-8 |

| Table 11-6  | Integration FIFO 0 bit assignments      | . 11-9 |

| Table 11-7  | ITATBCTR2 bit assignments               | 11-10  |

| Table 11-8  | Integration FIFO 1 Data bit assignments | 11-10  |

| Table 11-9  | ITATBCTR0 bit assignments               | 11-11  |

| Table 11-10 | TPIU_ITCTRL bit assignments             | 11-12  |

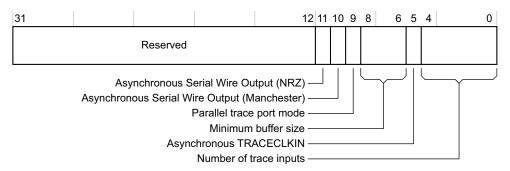

| Table 11-11 | TPIU_DEVID bit assignments              | 11-12  |

| Table A-1   | Differences between issue E and issue F | A-1    |

| Table A-2   | Differences between issue F and issue G |        |

| Table A-3   | Differences between issue G and issue H | A-5    |

# List of Figures Cortex-M3 Technical Reference Manual

| Figure 2-1   | Cortex-M3 block diagram                 |       |

|--------------|-----------------------------------------|-------|

| Figure 3-1   | System address map                      | 3-11  |

| Figure 3-2   | Bit-band mapping                        |       |

| Figure 3-3   | Processor register set                  |       |

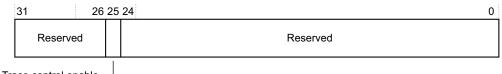

| Figure 4-1   | ACTLR bit assignments                   |       |

| Figure 4-2   | CPUID bit assignments                   |       |

| Figure 4-3   | AFSR bit assignments                    |       |

| Figure 6-1   | ICTR bit assignments                    |       |

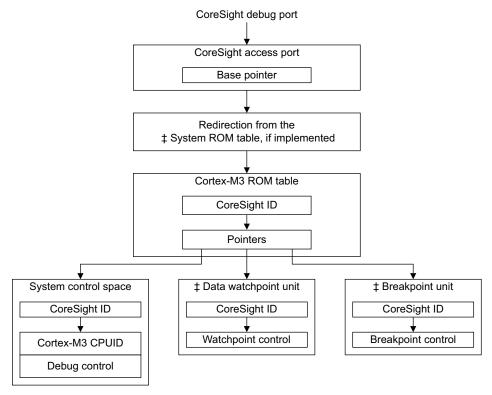

| Figure 7-1   | CoreSight discovery                     |       |

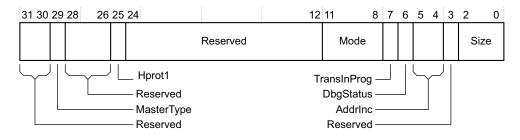

| Figure 7-2   | CSW bit assignments                     |       |

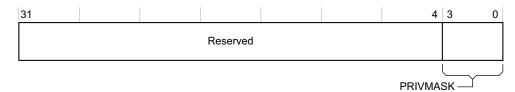

| Figure 9-1   | ITM_TPR bit assignments                 |       |

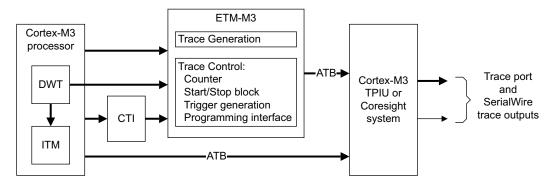

| Figure 10-1  | ETM block diagram                       | 10-3  |

| Figure 10-2  | ETMCR bit assignments                   | 10-11 |

| Figure 10-3  | ETMCCR bit assignments                  | 10-13 |

| Figure 10-4  | ETMSCR bit assignments                  | 10-14 |

| Figure 10-5  | ETMTECR1 bit assignments                | 10-15 |

| Figure 10-6  | ETMIDR bit assignments                  | 10-16 |

| Figure 10-7  | ETMCCER bit assignments                 | 10-17 |

| Figure 10-8  | ETMTESSEICR bit assignments             | 10-18 |

| Figure 10-9  | ETMPDSR bit assignments                 | 10-19 |

| Figure 10-10 | ITMISCIN bit assignments                |       |

| Figure 10-11 | ITTRIGOUT bit assignments               | 10-20 |

| Figure 10-12 | ETM_ITATBCTR2 bit assignments           | 10-20 |

| Figure 10-13 | ETM_ITATBCTR0 bit assignments           | 10-21 |

| Figure 11-1  | TPIU block diagram                      | 11-3  |

| Figure 11-2  | TPIU_ACPR bit assignments               | 11-6  |

| Figure 11-3  | TPIU_FFSR bit assignments               | 11-6  |

| Figure 11-4  | TPIU_FFCR bit assignments               | 11-7  |

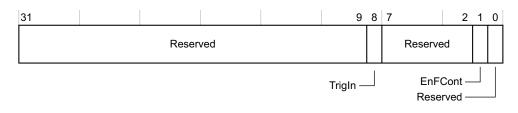

| Figure 11-5  | TRIGGER bit assignments                 | 11-8  |

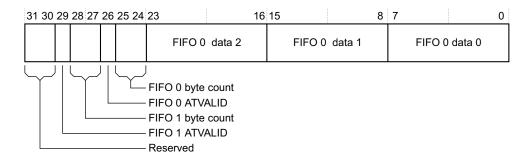

| Figure 11-6  | Integration FIFO 0 Data bit assignments | 11-9  |

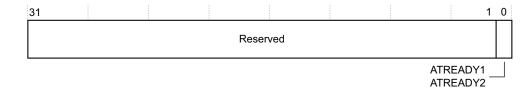

| Figure 11-7  | ITATBCTR2 bit assignments               | . 11-9 |

|--------------|-----------------------------------------|--------|

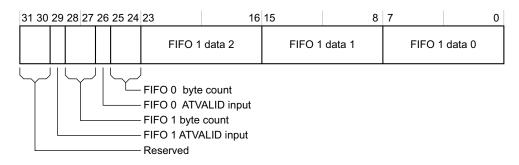

| Figure 11-8  | Integration FIFO 1 Data bit assignments | 11-10  |

| Figure 11-9  | ITATBCTR0 bit assignments               | 11-11  |

| Figure 11-10 | TPIU_ITCTRL bit assignments             | 11-11  |

| Figure 11-11 | TPIU_DEVID bit assignments              | 11-12  |

# Preface

This preface introduces the *Cortex-M3 Technical Reference Manual* (TRM). It contains the following sections:

- *About this book* on page x

- *Feedback* on page xiii.

## About this book

This book is for the Cortex-M3 processor. **Product revision status** The *rnpn* identifier indicates the revision status of the product described in this manual, where: Identifies the major revision of the product. r*n* Identifies the minor revision or modification status of the product. pn Intended audience This manual is written to help system designers, system integrators, verification engineers, and software programmers who are implementing a System-on-Chip (SoC) device based on the Cortex-M3 processor. Using this book This book is organized into the following chapters: **Chapter 1** Introduction Read this for a description of the components of the processor, and of the product documentation. **Chapter 2** Functional Description Read this for a description of the functionality of the processor. **Chapter 3** Programmers Model Read this for a description of the processor register set, modes of operation, and other information for programming the processor. Chapter 4 System Control Read this for a description of the registers and programmers model for system control. Chapter 5 Memory Protection Unit Read this for a description of the Memory Protection Unit (MPU). **Chapter 6** Nested Vectored Interrupt Controller Read this for a description of the interrupt processing and control. Chapter 7 Debug Read this for information about debugging and testing the processor core. Chapter 8 Data Watchpoint and Trace Unit Read this for a description of the Data Watchpoint and Trace (DWT) unit. **Chapter 9** Instrumentation Trace Macrocell Unit Read this for a description of the Instrumentation Trace Macrocell (ITM) unit. Chapter 10 Embedded Trace Macrocell Read this for a description of the processor Embedded Trace Macrocell (ETM). Chapter 11 Trace Port Interface Unit Read this for a description of the Trace Port Interface Unit (TPIU).

#### Appendix A Revisions

Read this for a description of the technical changes between released issues of this book.

**Glossary** Read this for definitions of terms used in this book.

#### Conventions

Conventions that this book can use are described in:

Typographical

#### Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.      |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file<br>and program names, and source code.                             |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter<br>the underlined text instead of the full command or option name. |

| monospace italic  | Denotes arguments to monospace text where the argument is to be<br>replaced by a specific value.                                           |

| monospace         | Denotes language keywords when used outside example code.                                                                                  |

| < and >           | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:                                   |

|                   | ADD Rd, Rn, <op2></op2>                                                                                                                    |

#### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- ARMv7-M Architecture Reference Manual (ARM DDI 0403)

- ARM Cortex-M3 Integration and Implementation Manual (ARM DII 0240)

- ARM AMBA<sup>®</sup> 3 AHB-Lite Protocol (v1.0) (ARM IHI 0033)

- ARM AMBA<sup>™</sup> 3 APB Protocol Specification (ARM IHI 0024)

- AMBA 3 ATB Protocol Specification (ARM IHI 0032)

- ARM CoreSight<sup>™</sup> Components Technical Reference Manual (ARM DDI 0314)

- ARM Debug Interface v5 Architecture Specification (ARM IHI 0031)

- ARM Embedded Trace Macrocell Architecture Specification (ARM IHI 0014).

## Other publications

٠

This section lists relevant documents published by third parties:

IEEE Standard Test Access Port and Boundary-Scan Architecture 1149.1-2001 (JTAG).

# Feedback

ARM welcomes feedback on this product and its documentation.

## Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on this manual

If you have comments on content then send e-mail to errata@arm.com. Give:

- the title

- the number, doc\_number-draft\_indicator

- the page number(s) to which your comments refer

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# Chapter 1 Introduction

This chapter introduces the processor and instruction set. It contains the following sections:

- *About the processor* on page 1-2

- *Features* on page 1-3

- *Interfaces* on page 1-4

- *Configurable options* on page 1-5

- *Product documentation* on page 1-6

- *Product revisions* on page 1-9.

# 1.1 About the processor

The Cortex-M3 is a low-power processor that features low gate count, low interrupt latency, and low-cost debug. It is intended for deeply embedded applications that require FIQ interrupt response features.

## 1.2 Features

The Cortex-M3 processor incorporates:

- a processor core

- a *Nested Vectored Interrupt Controller* (NVIC) closely integrated with the processor core to achieve low latency interrupt processing

- multiple high-performance bus interfaces

- a low-cost debug solution with the optional ability to:

- implement breakpoints and code patches

- implement watchpoints, tracing, and system profiling

- support printf style debugging

- bridge to a *Trace Port Analyzer* (TPA).

- an optional *Memory Protection Unit* (MPU)

- an optional ETM that enables reconstruction of program execution.

# 1.3 Interfaces

The processor has the following external interfaces:

- multiple memory and device bus interfaces

- ETM interface

- trace port interface

- debug port interface

- if the implementation includes an ETM, a Cross Trigger Interface (CTI).

# 1.4 Configurable options

You can configure your Cortex-M3 implementation to include the following optional components:

- MPU. See Chapter 5 Memory Protection Unit.

- Flash Patch and Breakpoint Unit (FPB). See Chapter 7 Debug.

- DWT. See Chapter 8 Data Watchpoint and Trace Unit.

- ITM. See Chapter 9 Instrumentation Trace Macrocell Unit.

- ETM. See Chapter 10 Embedded Trace Macrocell.

- Advanced High-performance Bus Access Port (AHB-AP). See Chapter 7 Debug.

- *AHB Trace Macrocell* (HTM) interface. See *AHB Trace Macrocell interface* on page 2-5.

- TPIU. See Chapter 11 Trace Port Interface Unit.

- *Wake-up Interrupt Controller* (WIC). See *Low power modes* on page 6-3.

- Debug Port. See *Debug port AHB-AP interface* on page 2-5.

— Note —

You can only configure trace functionality in the following combinations:

- no trace functionality

- ITM and DWT

- ITM, DWT, and ETM

- ITM, DWT, ETM, and HTM.

You can configure the debug features provided in the DWT independently.

## 1.5 Product documentation

This section describes the processor books, how they relate to the design flow, and the relevant architectural standards and protocols.

See *Additional reading* on page xi for more information about the books described in this section.

#### 1.5.1 Documentation

The Cortex-M3 documentation is as follows:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the Cortex-M3. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that the Cortex-M3 is implemented and integrated. If you are programming the Cortex-M3 then contact:

- the implementor to determine:

- the build configuration of the implementation

- what integration, if any, was performed before implementing the processor.

- the integrator to determine the pin configuration of the SoC that you are using.

#### **Integration and Implementation Manual**

The Integration and Implementation Manual (IIM) describes:

- The available build configuration options and related issues in selecting them.

- How to configure the *Register Transfer Level* (RTL) with the build configuration options

- How to integrate the processor into a SoC. This includes a description of the integration kit and describes the pins that the integrator must tie off to configure the macrocell for the required integration.

- How to implement the processor into your design. This includes floorplanning guidelines, Design for Test (DFT) information, and how to perform netlist dynamic verification on the processor.

- The processes to sign off the integration and implementation of the design.

The ARM product deliverables include reference scripts and information about using them to implement your design.

Reference methodology documentation from your EDA tools vendor complements the IIM.

The IIM is a confidential book that is only available to licensees.

#### **Cortex-M3 User Guide Reference Material**

This document provides reference material that ARM partners can configure and include in a User Guide for an ARM Cortex-M3 processor. Typically:

- each chapter in this reference material might correspond to a section in the User Guide

- each top-level section in this reference material might correspond to a chapter in the User Guide.

However, ARM partners can organize this material in any way, subject to the conditions of the licence agreement under which ARM supplied the material.

#### 1.5.2 Design Flow

The processor is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following process:

#### Implementation

The implementor configures and synthesizes the RTL to produce a hard macrocell. This might include integrating RAMs into the design.

**Integration** The integrator connects the implemented design into a SoC. This includes connecting it to a memory system and peripherals.

#### Programming

The system programmer develops the software required to configure and initialize the processor, and tests the required application software.

Each stage in the process can be performed by a different party. Implementation and integration choices affect the behavior and features of the processor.

For MCUs, often a single design team integrates the processor before synthesizing the complete design. Alternatively, the team can synthesise the processor on its own or partially integrated, to produce a macrocell that is then integrated, possibly by a separate team.

The operation of the final device depends on:

#### **Build configuration**

The implementor chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

#### **Configuration inputs**

The integrator configures some features of the processor by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

#### Software configuration

The programmer configures the processor by programming particular values into registers. This affects the behavior of the processor.

#### — Note –

This manual refers to implementation-defined features that are applicable to build configuration options. Reference to a feature that is included means that the appropriate build and pin configuration options are selected. Reference to an enabled feature means one that has also been configured by software.

#### 1.5.3 Architecture and protocol information

The processor complies with, or implements, the specifications described in:

- ARM architecture on page 1-8

- Bus architecture on page 1-8

- Debug on page 1-8

#### Embedded Trace Macrocell.

This book complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

## ARM architecture

The processor implements the ARMv7-M architecture profile. See the *ARMv7-M Architecture Reference Manual*.

For more information about architectural compliance, see Architecture and protocol information on page 1-9.

#### **Bus architecture**

The processor provides three primary bus interfaces implementing a variant of the AMBA 3 AHB-Lite protocol. The processor implements an interface for CoreSight and other debug components using the AMBA 3 APB protocol. See

- the ARM AMBA 3 AHB-Lite Protocol (v1.0)

- the ARM AMBA 3 APB Protocol Specification.

#### Debug

The debug features of the processor implement the ARM debug interface architecture. See the *ARM Debug Interface v5 Architecture Specification*. The processor also implements debug features defined by the ARMv7-M. See the *ARMv7-M Architecture Reference Manual*.

#### **Embedded Trace Macrocell**

The trace features of the processor implement version 3.4 of the ARM Embedded Trace Macrocell architecture. See the *ARM Embedded Trace Macrocell Architecture Specification*.

# 1.6 Product revisions

This section summarizes the differences in functionality between the different releases of this processor:

- Differences in functionality between r0p0 and r1p0

- Differences in functionality between r1p0 and r1p1

- *Differences in functionality between r1p1 and r2p0* on page 1-10.

#### 1.6.1 Differences in functionality between r0p0 and r1p0

•

In summary, the differences in functionality include:

- Addition of configurable data value comparison to the DWT module.

- Addition of a MATCHED bit to **DWT\_FUNCTION**.

- Addition of configurable **ETMFIFOFULL** stalling functionality to the processor and the ETM.

- Addition of SWV Mode to the ITM.

- CPUID Base Register VARIANT field changed to indicate Rev1.

- Cortex-M3 Rev0 Bit-band accesses in BE8 mode required access sizes to be byte. Cortex-M3 Rev1 has been changed so that BE8 bit-band accesses function with any access size.

- Addition of a configuration bit called STKALIGN to ensure that all exceptions have eight-byte stack alignment.

- Addition of the Auxiliary Fault Status Register at address 0xE000ED3C. To set this register, a 32-bit input bus called AUXFAULT has been added.

- Addition of HTM support.

- ICode and DCode cacheable and bufferable HPROT values permanently tied to write-through.

- Addition of the SWJ-DP. This is the standard CoreSight<sup>™</sup> debug port that combines JTAG-DP and SW-DP.

- Addition of DWT\_PCSR Register at address 0xE000101C.

- Errata fixes to the r0p0 release.

#### 1.6.2 Differences in functionality between r1p0 and r1p1

In summary, the differences in functionality include:

- Data value matching for watchpoint generation has been made implementation time configurable.

- Architectural clock gating in the ETM is configurable at implementation.

- **DAPCLKEN** was required to be a static signal in r0p0 and r1p0. This requirement has been removed for r1p1.

- **SLEEPING** signal now suppressed until current outstanding instruction fetch has completed.

- Errata fixes to the r1p0 release.

#### 1.6.3 Differences in functionality between r1p1 and r2p0

In summary, the differences in functionality include:

- Implementation time options have been added to select between different levels of debug and trace support. This has replaced the previous TIEOFF\_FPBEN and TIEOFF\_TRCENA options.

- New implementation option to enable the resetting of all registers within the processor.

- Architectural clock gating inclusion is now controlled using one implementation option.

- **DBGRESTART** input and **DBGRESTARTED** output have been added for use in debugging multi-core systems. See the *ARMv7-M Architecture Reference Manual* for more information.

- **SLEEPHOLDREQn** input and **SLEEPHOLDACKn** have been added to enable the extension of SLEEPING.

- The APB interface has been upgraded from v2.0 to v3.0.

- A new output signal called **INTERNALSTATE** has been added that enables observation of some of the internal state of the core if the OBSERVATION implementation option is used.

- Added support for fault-robust implementations.

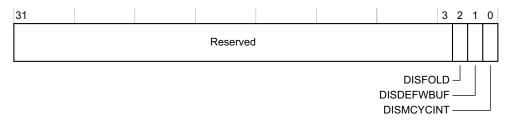

- An Auxiliary Control Register has been added with new functionality disable bits to:

- stop interruption of load/store multiples, divides and multiplies

- stop IT folding

- disable the write buffers in Cortex-M3 for default memory map accesses.

- The STKALIGN bit reset value in the Configuration and Control Register at address 0xE000ED14 has been inverted. The reset value is now 1, which means that the stack frame is 8-byte aligned by default.

- Addition of a Wake-up Interrupt Controller to minimize logic in the always clocked domain during sleep.

- Addition of **FIXHMASTERTYPE** pin to prevent debugger marking AHB transactions as core data side if required.

- Errata fixes to the r1p1 release.

# Chapter 2 Functional Description

This chapter introduces the processor and its external interfaces. It contains the following sections:

- *About the functions* on page 2-2

- *Interfaces* on page 2-4.

# 2.1 About the functions

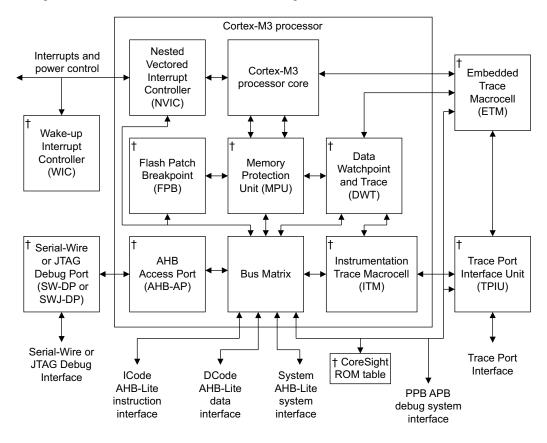

Figure 2-1 shows the structure of the Cortex-M3 processor.

† Optional component

#### Figure 2-1 Cortex-M3 block diagram

The Cortex-M3 processor features:

- A low gate count processor core, with low latency interrupt processing that has:

- A subset of the Thumb instruction set, defined in the *ARMv7-M Architecture Reference Manual*.

- Banked Stack Pointer (SP).

- Hardware divide instructions, SDIV and UDIV.

- Handler and Thread modes.

- Thumb and Debug states.

- Support for interruptible-continued instructions LDM, STM, PUSH, and POP for low interrupt latency.

- Automatic processor state saving and restoration for low latency *Interrupt Service Routine* (ISR) entry and exit.

- Support for ARMv6 big-endian byte-invariant or little-endian accesses.

- Support for ARMv6 unaligned accesses.

- *Nested Vectored Interrupt Controller* (NVIC) closely integrated with the processor core to achieve low latency interrupt processing. Features include:

- External interrupts, configurable from 1 to 240.

- Bits of priority, configurable from 3 to 8.

- Dynamic reprioritization of interrupts.

- Priority grouping. This enables selection of preempting interrupt levels and non

preempting interrupt levels.

- Support for tail-chaining and late arrival of interrupts. This enables back-to-back interrupt processing without the overhead of state saving and restoration between interrupts.

- Processor state automatically saved on interrupt entry, and restored on interrupt exit, with no instruction overhead.

- Optional *Wake-up Interrupt Controller* (WIC), providing ultra-low power sleep mode support.

- Memory Protection Unit (MPU). An optional MPU for memory protection, including:

- Eight memory regions.

- Sub Region Disable (SRD), enabling efficient use of memory regions.

- The ability to enable a background region that implements the default memory map attributes.

- Bus interfaces:

- Three Advanced High-performance Bus-Lite (AHB-Lite) interfaces: ICode, DCode, and System bus interfaces.

- Private Peripheral Bus (PPB) based on Advanced Peripheral Bus (APB) interface.

- Bit-band support that includes atomic bit-band write and read operations.

- Memory access alignment.

- Write buffer for buffering of write data.

- Exclusive access transfers for multiprocessor systems.

- Low-cost debug solution that features:

- Debug access to all memory and registers in the system, including access to memory mapped devices, access to internal core registers when the core is halted, and access to debug control registers even while SYSRESETn is asserted.

- Serial Wire Debug Port (SW-DP) or Serial Wire JTAG Debug Port (SWJ-DP) debug access, or both.

- Optional *Flash Patch and Breakpoint* (FPB) unit for implementing breakpoints and code patches.

- Optional *Data Watchpoint and Trace* (DWT) unit for implementing watchpoints, data tracing, and system profiling.

- Optional *Instrumentation Trace Macrocell* (ITM) for support of printf style debugging.

- Optional *Trace Port Interface Unit* (TPIU) for bridging to a *Trace Port Analyzer* (TPA), including *Single Wire Output* (SWO) mode.

- Optional *Embedded Trace Macrocell* (ETM) for instruction trace.

## 2.2 Interfaces

The processor contains the following external interfaces:

- bus interfaces

- *ETM interface* on page 2-5

- AHB Trace Macrocell interface on page 2-5

- *Debug port AHB-AP interface* on page 2-5.

#### 2.2.1 Bus interfaces

The processor contains four external *Advanced High-performance Bus* (AHB)-Lite bus interfaces:

#### ICode memory interface

Instruction fetches from Code memory space, 0x00000000 to 0x1FFFFFF, are performed over this 32-bit AHB-Lite bus.

The Debugger cannot access this interface. All fetches are word-wide. The number of instructions fetched per word depends on the code running and the alignment of the code in memory.

#### DCode memory interface

Data and debug accesses to Code memory space, 0x00000000 to 0x1FFFFFF, are performed over this 32-bit AHB-Lite bus. Core data accesses have a higher priority than debug accesses on this bus. This means that debug accesses are waited until core accesses have completed when there are simultaneous core and debug access to this bus.

Control logic in this interface converts unaligned data and debug accesses into two or three aligned accesses, depending on the size and alignment of the unaligned access. This stalls any subsequent data or debug access until the unaligned access has completed.

—— Note ——

ARM strongly recommends that any external arbitration between the ICode and DCode AHB bus interfaces ensures that DCode has a higher priority than ICode.

#### System interface

Instruction fetches, and data and debug accesses, to address ranges 0x2000000 to 0xDFFFFFF and 0xE0100000 to 0xFFFFFFF are performed over this 32-bit AHB-Lite bus.

For simultaneous accesses to this bus, the arbitration order in decreasing priority is:

- data accesses

- instruction and vector fetches

- debug.

The system bus interface contains control logic to handle unaligned accesses, FPB remapped accesses, bit-band accesses, and pipelined instruction fetches.

#### **Private Peripheral Bus (PPB)**

Data and debug accesses to external PPB space, 0xE0040000 to 0xE00FFFFF, are performed over this 32-bit *Advanced Peripheral Bus* (APB) bus. The *Trace Port Interface Unit* (TPIU) and vendor specific peripherals are on this bus.

Core data accesses have higher priority than debug accesses, so debug accesses are waited until core accesses have completed when there are simultaneous core and debug access to this bus. Only the address bits necessary to decode the External PPB space are supported on this interface.

#### 2.2.2 ETM interface

The ETM interface enables simple connection of an ETM to the processor. It provides a channel for instruction trace to the ETM. See the *ARM Embedded Trace Macrocell Architecture Specification*.

#### 2.2.3 AHB Trace Macrocell interface

The *AHB Trace Macrocell* (HTM) interface enables a simple connection of the AHB trace macrocell to the processor. It provides a channel for the data trace to the HTM.

Your implementation must include this interface to use the HTM interface. You must set TRCENA to 1 in the Debug Exception and Monitor Control Register (DEMCR) before you enable the HTM to enable the HTM port to supply trace data. See the *ARMv7-M Architecture Reference Manual*.

#### 2.2.4 Debug port AHB-AP interface

The processor contains an *Advanced High-performance Bus Access Port* (AHB-AP) interface for debug accesses. An external *Debug Port* (DP) component accesses this interface. The Cortex-M3 system supports three possible DP implementations:

- The Serial Wire JTAG Debug Port (SWJ-DP). The SWJ-DP is a standard CoreSight debug port that combines JTAG-DP and Serial Wire Debug Port (SW-DP).

- The SW-DP. This provides a two-pin interface to the AHB-AP port.

- No DP present. If no debug functionality is present within the processor, a DP is not required.

The two DP implementations provide different mechanisms for debug access to the processor. Your implementation must contain only one of these components.

— Note — — —

Your implementation might contain an alternative implementor-specific DP instead of SW-DP or SWJ-DP. See your implementor for details.

For more detailed information on the DP components, see the *CoreSight Components Technical Reference manual*.

For more information on the AHB-AP, see Chapter 7 Debug.

The DP and AP together are referred to as the Debug Access Port (DAP).

For more detailed information on the debug interface, see the *ARM Debug Interface v5 Architecture Specification*.

# Chapter 3 Programmers Model

This chapter describes the processor programmers model. It contains the following sections:

- *About the programmers model* on page 3-2

- *Modes of operation and execution* on page 3-3

- *Instruction set summary* on page 3-4

- System address map on page 3-11

- Write buffer on page 3-14

- *Bit-banding* on page 3-16

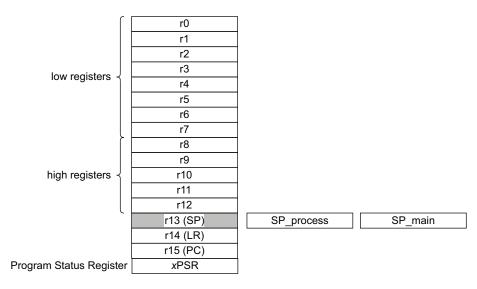

- Processor core register summary on page 3-18

- *Exceptions* on page 3-20.

# 3.1 About the programmers model

The *ARMv7-M Architecture Reference Manual* provides a complete description of the programmers model. This chapter gives an overview of the Cortex-M3 processor programmers model that describes the implementation-defined options. It also contains the ARMv7-M Thumb instructions it uses and their cycle counts for the processor. In addition:

- Chapter 4 summarizes the system control features of the programmers model

- Chapter 5 summarizes the MPU features of the programmers model

- Chapter 6 summarizes the NVIC features of the programmers model

- Chapter 7 summarizes the Debug features of the programmers model

- Chapter 8 summarizes the DWT features of the programmers model

- Chapter 9 summarizes the ITM features of the programmers model

- Chapter 10 summarizes the ETM features of the programmers model

- Chapter 11 summarizes the TPIU features of the programmers model.

# 3.2 Modes of operation and execution

This section briefly describes the modes of operation and execution of the Cortex-M3 processor. See the *ARMv7-M Architecture Reference Manual* for more information.

#### 3.2.1 Operating modes

The processor supports two modes of operation, Thread mode and Handler mode:

- The processor enters Thread mode on Reset, or as a result of an exception return. Privileged and Unprivileged code can run in Thread mode.

- The processor enters Handler mode as a result of an exception. All code is privileged in Handler mode.

#### 3.2.2 Operating states

The processor can operate in one of two operating states:

- Thumb state. This is normal execution running 16-bit and 32-bit halfword aligned Thumb instructions.

- Debug State. This is the state when the processor is in halting debug.

#### 3.2.3 Privileged access and user access

Code can execute as privileged or unprivileged. Unprivileged execution limits or excludes access to some resources. Privileged execution has access to all resources. Handler mode is always privileged. Thread mode can be privileged or unprivileged.

# 3.3 Instruction set summary

This section provides information on:

- Cortex-M3 instructions

- Load/store timings on page 3-8

- Binary compatibility with other Cortex processors on page 3-9.

#### 3.3.1 Cortex-M3 instructions

The processor implements the ARMv7-M Thumb instruction set. Table 3-1 shows the Cortex-M3 instructions and their cycle counts. The cycle counts are based on a system with zero wait states.

Within the assembler syntax, depending on the operation, the <op2> field can be replaced with one of the following options:

- a simple register specifier, for example Rm

- an immediate shifted register, for example Rm, LSL #4

- a register shifted register, for example Rm, LSL Rs

- an immediate value, for example #0xE000E000.

For brevity, not all load and store addressing modes are shown. See the *ARMv7-M Architecture Reference Manual* for more information.

Table 3-1 uses the following abbreviations in the Cycles column:

- **P** The number of cycles required for a pipeline refill. This ranges from 1 to 3 depending on the alignment and width of the target instruction, and whether the processor manages to speculate the address early.

- **B** The number of cycles required to perform the barrier operation. For DSB and DMB, the minimum number of cycles is zero. For ISB, the minimum number of cycles is equivalent to the number required for a pipeline refill.

- N The number of registers in the register list to be loaded or stored, including PC or LR.

- W The number of cycles spent waiting for an appropriate event.

#### Table 3-1 Cortex-M3 instruction set summary

| Operation | Description        | Assembler               | Cycles |

|-----------|--------------------|-------------------------|--------|

| Move      | Register           | MOV Rd, <op2></op2>     | 1      |

|           | 16-bit immediate   | MOVW Rd, # <imm></imm>  | 1      |

|           | Immediate into top | MOVT Rd, # <imm></imm>  | 1      |

|           | To PC              | MOV PC, Rm              | 1 + P  |

| Add       | Add                | ADD Rd, Rn, <op2></op2> | 1      |

|           | Add to PC          | ADD PC, PC, Rm          | 1 + P  |

|           | Add with carry     | ADC Rd, Rn, <op2></op2> | 1      |

|           | Form address       | ADR Rd, <label></label> | 1      |

| Table 3-1 Cortex-M3 | instruction set | summary | (continued) |

|---------------------|-----------------|---------|-------------|

|---------------------|-----------------|---------|-------------|

| Operation | Description              | Assembler                           | Cycles               |

|-----------|--------------------------|-------------------------------------|----------------------|

| Subtract  | Subtract                 | SUB Rd, Rn, <op2></op2>             | 1                    |

|           | Subtract with borrow     | SBC Rd, Rn, <op2></op2>             | 1                    |

|           | Reverse                  | RSB Rd, Rn, <op2></op2>             | 1                    |

| Multiply  | Multiply                 | MUL Rd, Rn, Rm                      | 1                    |

|           | Multiply accumulate      | MLA Rd, Rn, Rm                      | 2                    |

|           | Multiply subtract        | MLS Rd, Rn, Rm                      | 2                    |

|           | Long signed              | SMULL RdLo, RdHi, Rn, Rm            | 3 to 5 <sup>a</sup>  |

|           | Long unsigned            | UMULL RdLo, RdHi, Rn, Rm            | 3 to 5 <sup>a</sup>  |

|           | Long signed accumulate   | SMLAL RdLo, RdHi, Rn, Rm            | 4 to 7 <sup>a</sup>  |

|           | Long unsigned accumulate | UMLAL RdLo, RdHi, Rn, Rm            | 4 to 7 <sup>a</sup>  |

| Divide    | Signed                   | SDIV Rd, Rn, Rm                     | 2 to 12 <sup>b</sup> |

|           | Unsigned                 | UDIV Rd, Rn, Rm                     | 2 to 12 <sup>b</sup> |

| Saturate  | Signed                   | SSAT Rd, # <imm>, <op2></op2></imm> | 1                    |

|           | Unsigned                 | USAT Rd, # <imm>, <op2></op2></imm> | 1                    |

| Compare   | Compare                  | CMP Rn, <op2></op2>                 | 1                    |

|           | Negative                 | CMN Rn, <op2></op2>                 | 1                    |

| Logical   | AND                      | AND Rd, Rn, <op2></op2>             | 1                    |

|           | Exclusive OR             | EOR Rd, Rn, <op2></op2>             | 1                    |

|           | OR                       | ORR Rd, Rn, <op2></op2>             | 1                    |

|           | OR NOT                   | ORN Rd, Rn, <op2></op2>             | 1                    |

|           | Bit clear                | BIC Rd, Rn, <op2></op2>             | 1                    |

|           | Move NOT                 | MVN Rd, <op2></op2>                 | 1                    |

|           | AND test                 | TST Rn, <op2></op2>                 | 1                    |

|           | Exclusive OR test        | TEQ Rn, <op1></op1>                 |                      |

| Shift     | Logical shift left       | LSL Rd, Rn, # <imm></imm>           | 1                    |

|           | Logical shift left       | LSL Rd, Rn, Rs                      | 1                    |

|           | Logical shift right      | LSR Rd, Rn, # <imm></imm>           | 1                    |

|           | Logical shift right      | LSR Rd, Rn, Rs                      | 1                    |

|           | Arithmetic shift right   | ASR Rd, Rn, # <imm></imm>           | 1                    |

|           | Arithmetic shift right   | ASR Rd, Rn, Rs                      | 1                    |

| Table 3-1 Cortex-M3 | instruction se | et summary | (continued) |

|---------------------|----------------|------------|-------------|

|---------------------|----------------|------------|-------------|

| Operation | Description           | Assembler                          | Cycles      |

|-----------|-----------------------|------------------------------------|-------------|

| Rotate    | Rotate right          | ROR Rd, Rn, # <imm></imm>          | 1           |

|           | Rotate right          | ROR Rd, Rn, Rs                     | 1           |

|           | With extension        | RRX Rd, Rn                         | 1           |

| Count     | Leading zeroes        | CLZ Rd, Rn                         | 1           |

| Load      | Word                  | LDR Rd, [Rn, <op2>]</op2>          | 2°          |

|           | To PC                 | LDR PC, [Rn, <op2>]</op2>          | $2^{c} + P$ |

|           | Halfword              | LDRH Rd, [Rn, <op2>]</op2>         | 2°          |

|           | Byte                  | LDRB Rd, [Rn, <op2>]</op2>         | 2°          |

|           | Signed halfword       | LDRSH Rd, [Rn, <op2>]</op2>        | 2°          |

|           | Signed byte           | LDRSB Rd, [Rn, <op2>]</op2>        | 2°          |

|           | User word             | LDRT Rd, [Rn, # <imm>]</imm>       | 2°          |

|           | User halfword         | LDRHT Rd, [Rn, # <imm>]</imm>      | 2°          |

|           | User byte             | LDRBT Rd, [Rn, # <imm>]</imm>      | 2°          |

|           | User signed halfword  | LDRSHT Rd, [Rn, # <imm>]</imm>     | 2°          |

|           | User signed byte      | LDRSBT Rd, [Rn, # <imm>]</imm>     | 2°          |

|           | PC relative           | LDR Rd,[PC, # <imm>]</imm>         | 2°          |

|           | Doubleword            | LDRD Rd, Rd, [Rn, # <imm>]</imm>   | 1 + N       |

|           | Multiple              | LDM Rn, { <reglist>}</reglist>     | 1 + N       |

|           | Multiple including PC | LDM Rn, { <reglist>, PC}</reglist> | 1 + N + F   |

| Store     | Word                  | STR Rd, [Rn, <op2>]</op2>          | 2°          |

|           | Halfword              | STRH Rd, [Rn, <op2>]</op2>         | 2°          |

|           | Byte                  | STRB Rd, [Rn, <op2>]</op2>         | 2°          |

|           | Signed halfword       | STRSH Rd, [Rn, <op2>]</op2>        | 2°          |

|           | Signed byte           | STRSB Rd, [Rn, <op2>]</op2>        | 2°          |

|           | User word             | STRT Rd, [Rn, # <imm>]</imm>       | 2°          |

|           | User halfword         | STRHT Rd, [Rn, # <imm>]</imm>      | 2°          |

|           | User byte             | STRBT Rd, [Rn, # <imm>]</imm>      | 2°          |

|           | User signed halfword  | STRSHT Rd, [Rn, # <imm>]</imm>     | 2°          |

|           | User signed byte      | STRSBT Rd, [Rn, # <imm>]</imm>     | 2°          |

|           | Doubleword            | STRD Rd, Rd, [Rn, # <imm>]</imm>   | 1 + N       |

|           | Multiple              | STM Rn, { <reglist>}</reglist>     | 1 + N       |

| Table 3-1 Cortex-M3 instruction set summary (continued |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Operation    | Description             | Assembler                                | Cycles     |

|--------------|-------------------------|------------------------------------------|------------|

| Push         | Push                    | PUSH { <reglist>}</reglist>              | 1 + N      |

|              | Push with link register | PUSH { <reglist>, LR}</reglist>          | 1 + N      |

| Рор          | Рор                     | <pre>POP {<reglist>}</reglist></pre>     | 1 + N      |

|              | Pop and return          | <pre>POP {<reglist>, PC}</reglist></pre> | 1 + N + P  |

| Semaphore    | Load exclusive          | LDREX Rd, [Rn, # <imm>]</imm>            | 2          |

|              | Load exclusive half     | LDREXH Rd, [Rn]                          | 2          |

|              | Load exclusive byte     | LDREXB Rd, [Rn]                          | 2          |

|              | Store exclusive         | STREX Rd, Rt, [Rn, # <imm>]</imm>        | 2          |

|              | Store exclusive half    | STREXH Rd, Rt, [Rn]                      | 2          |

|              | Store exclusive byte    | STREXB Rd, Rt, [Rn]                      | 2          |

|              | Clear exclusive monitor | CLREX                                    | 1          |

| Branch       | Conditional             | B <cc> <label></label></cc>              | 1 or 1 + P |

|              | Unconditional           | B <label></label>                        | 1 + P      |

|              | With link               | BL <label></label>                       | 1 + P      |

|              | With exchange           | BX Rm                                    | 1 + P      |

|              | With link and exchange  | BLX Rm                                   | 1 + P      |

|              | Branch if zero          | CBZ Rn, <label></label>                  | 1 or 1 + P |

|              | Branch if non-zero      | CBNZ Rn, <label></label>                 | 1 or 1 + P |

|              | Byte table branch       | TBB [Rn, Rm]                             | 2 + P      |

|              | Halfword table branch   | TBH [Rn, Rm, LSL#1]                      | 2 + P      |

| State change | Supervisor call         | SVC # <imm></imm>                        | -          |

|              | If-then-else            | IT <cond></cond>                         | 1e         |

|              | Disable interrupts      | CPSID <flags></flags>                    | 1 or 2     |

|              | Enable interrupts       | CPSIE <flags></flags>                    | 1 or 2     |

|              | Read special register   | MRS Rd, <specreg></specreg>              | 1 or 2     |

|              | Write special register  | MSR <specreg>, Rn</specreg>              | 1 or 2     |

|              | Breakpoint              | BKPT # <imm></imm>                       | -          |

| Extend       | Signed halfword to word | SXTH Rd, <op2></op2>                     | 1          |

|              | Signed byte to word     | SXTB Rd, <op2></op2>                     | 1          |

|              | Unsigned halfword       | UXTH Rd, <op2></op2>                     | 1          |

|              | Unsigned byte           | UXTB Rd, <op2></op2>                     | 1          |

| Operation | Description                 | Assembler                                | Cycles |

|-----------|-----------------------------|------------------------------------------|--------|

| Bit field | Extract unsigned            | UBFX Rd, Rn, # <imm>, #<imm></imm></imm> | 1      |

|           | Extract signed              | SBFX Rd, Rn, # <imm>, #<imm></imm></imm> | 1      |

|           | Clear                       | BFC Rd, Rn, # <imm>, #<imm></imm></imm>  | 1      |

|           | Insert                      | BFI Rd, Rn, # <imm>, #<imm></imm></imm>  | 1      |

| Reverse   | Bytes in word               | REV Rd, Rm                               | 1      |

|           | Bytes in both halfwords     | REV16 Rd, Rm                             | 1      |

|           | Signed bottom halfword      | REVSH Rd, Rm                             | 1      |

|           | Bits in word                | RBIT Rd, Rm                              | 1      |

| Hint      | Send event                  | SEV                                      | 1      |

|           | Wait for event              | WFE                                      | 1 + W  |

|           | Wait for interrupt          | WFI                                      | 1 + W  |

|           | No operation                | NOP                                      | 1      |

| Barriers  | Instruction synchronization | ISB                                      | 1 + B  |

|           | Data memory                 | DMB                                      | 1 + B  |

|           | Data synchronization        | DSB <flags></flags>                      | 1 + B  |

#### Table 3-1 Cortex-M3 instruction set summary (continued)

a. UMULL, SMULL, UMLAL, and SMLAL instructions use early termination depending on the size of the source values. These are interruptible, that is abandoned and restarted, with worst case latency of one cycle.

- b. Division operations use early termination to minimize the number of cycles required based on the number of leading ones and zeroes in the input operands.

- c. Neighboring load and store single instructions can pipeline their address and data phases. This enables these instructions to complete in a single execution cycle.

- d. Conditional branch completes in a single cycle if the branch is not taken.

- e. An IT instruction can be folded onto a preceding 16-bit Thumb instruction, enabling execution in zero cycles.

#### 3.3.2 Load/store timings

This section describes how best to pair instructions to achieve more reductions in timing.

- STR Rx, [Ry,#imm] is always one cycle. This is because the address generation is performed in the initial cycle, and the data store is performed at the same time as the next instruction is executing. If the store is to the store buffer, and the store buffer is full or not enabled, the next instruction is delayed until the store can complete. If the store is not to the store buffer, for example to the Code segment, and that transaction stalls, the impact on timing is only felt if another load or store operation is executed before completion.

- LDR Rx!, [any] is not normally pipelined. That is, base update load is generally at least a two-cycle operation (more if stalled). However, if the next instruction does not require to read from a register, the load is reduced to one cycle. Non register writing instructions include CMP, TST, NOP, and non-taken IT controlled instructions.

- LDR PC, [any] is always a blocking operation. This means at least two cycles for the load, and three cycles for the pipeline reload. So this operation takes at least five cycles, or more if stalled on the load or the fetch.

- LDR Rx, [PC, #imm] might add a cycle because of contention with the fetch unit.

- TBB and TBH are also blocking operations. These are at least two cycles for the load, one cycle for the add, and three cycles for the pipeline reload. This means at least six cycles, or more if stalled on the load or the fetch.

- LDR [any] are pipelined when possible. This means that if the next instruction is an LDR or STR, and the destination of the first LDR is not used to compute the address for the next instruction, then one cycle is removed from the cost of the next instruction. So, an LDR might be followed by an STR, so that the STR writes out what the LDR loaded. More multiple LDRs can be pipelined together. Some optimized examples are:

- LDR R0, [R1]; LDR R1, [R2] normally three cycles total

- LDR R0, [R1, R2]; STR R0, [R3, #20] normally three cycles total

- LDR R0, [R1, R2]; STR R1, [R3, R2] normally three cycles total

- LDR R0, [R1, R5]; LDR R1, [R2]; LDR R2, [R3, #4] normally four cycles total.

- Other instructions cannot be pipelined after STR with register offset. STR can only be pipelined when it follows an LDR, but nothing can be pipelined after the store. Even a stalled STR normally only takes two cycles, because of the store buffer.

- LDREX and STREX can be pipelined exactly as LDR. Because STREX is treated more like an LDR, it can be pipelined as explained for LDR. Equally LDREX is treated exactly as an LDR and so can be pipelined.

- LDRD and STRD cannot be pipelined with preceding or following instructions. However, the two words are pipelined together. So, this operation requires three cycles when not stalled.

- LDM and STM cannot be pipelined with preceding or following instructions. However, all elements after the first are pipelined together. So, a three element LDM takes 2+1+1 or 5 cycles when not stalled. Similarly, an eight element store takes nine cycles when not stalled. When interrupted, LDM and STM instructions continue from where they left off when returned to. The continue operation adds one or two cycles to the first element when started.

- Unaligned word or halfword loads or stores add penalty cycles. A byte aligned halfword load or store adds one extra cycle to perform the operation as two bytes. A halfword aligned word load or store adds one extra cycle to perform the operation as two halfwords. A byte-aligned word load or store adds two extra cycles to perform the operation as a byte, a halfword, and a byte. These numbers increase if the memory stalls. A STR or STRH cannot delay the processor because of the store buffer.

## 3.3.3 Binary compatibility with other Cortex processors

The processor implements a binary compatible subset of the instruction set and features provided by other Cortex-M profile processors. You can move software, including system level software, from the Cortex-M3 processor to other Cortex-M profile processors.

To ensure a smooth transition, ARM recommends that code designed to operate on other Cortex-M profile processor architectures obey the following rules and configure the *Configuration Control Register* (CCR) appropriately:

- use word transfers only to access registers in the NVIC and System Control Space (SCS).

- treat all unused SCS registers and register fields on the processor as Do-Not-Modify.

- configure the following fields in the CCR:

- STKALIGN bit to 1

- UNALIGN\_TRP bit to 1

- Leave all other bits in the CCR register as their original value.

# 3.4 System address map

The processor contains a bus matrix that arbitrates the processor core and optional *Debug Access Port* (DAP) memory accesses to both the external memory system and to the internal *System Control Space* (SCS) and debug components.

Priority is always given to the processor to ensure that any debug accesses are as non-intrusive as possible. For a zero wait state system, all debug accesses to system memory, SCS, and debug resources are completely non-intrusive.

Figure 3-1 shows the system address map.

| 0xE0100000    |      |                 | -∼                    | <b>F</b>                   |          | 0xFFFFFFFF |

|---------------|------|-----------------|-----------------------|----------------------------|----------|------------|

| 0xE00FF000    |      | ROM Table       |                       | <b>o</b> 1                 |          |            |

| 0xE0042000    |      | External PPB    |                       | System                     |          |            |

| 0xE0041000    |      | ETM             | $\downarrow$ $\frown$ |                            |          | 0xE0100000 |

| 0xE0040000    |      | TPIU            |                       | Private peripheral bus - I | External |            |

|               |      |                 | >                     | <b>.</b>                   |          | 0xE0040000 |

| 0xE0040000    |      | Reserved        |                       | Private peripheral bus -   | Internal | 0,0000000  |

| 0xE000F000    |      | SCS             | - /                   |                            |          | 0xE0000000 |

| 0xE000E000    |      | Reserved        | - /                   |                            |          |            |

| 0xE0003000    |      | FPB             | - /                   | External device            | 1.0GB    |            |

| 0xE0002000    |      | DWT             | - /                   |                            |          |            |

| 0xE0001000    |      | ITM             |                       |                            |          |            |

| 0xE0000000    |      | I I IVI         |                       |                            |          | 0xA0000000 |

|               |      |                 |                       |                            |          |            |

| 0x44000000    |      |                 |                       |                            |          |            |

| 0,44000000    |      |                 | $\mathbb{N}$          | External RAM               | 1.0GB    |            |

|               | 32MB | Bit band alias  |                       |                            |          |            |

|               |      |                 |                       |                            |          |            |

| 0x42000000    |      |                 | -                     |                            |          | 0x60000000 |

|               | 31MB |                 |                       |                            |          |            |

| 0x40100000    |      |                 |                       | Peripheral                 | 0.5GB    |            |

| 0x40100000    | 1MB  | Bit band region |                       |                            |          |            |

| 0x24000000    |      |                 |                       |                            |          | 0x40000000 |

| 0/12 10000000 |      |                 | $\sim$                |                            | 0.500    |            |

|               | 32MB | Bit band alias  |                       | SRAM                       | 0.5GB    |            |

|               |      |                 |                       |                            |          |            |

| 0x22000000    |      |                 | 1 /                   |                            |          | 0x20000000 |

|               | 31MB |                 |                       |                            | 0.500    |            |

| 0x20100000    |      |                 |                       | Code                       | 0.5GB    |            |

| 0x20000000    | 1MB  | Bit band region |                       |                            |          |            |

|               |      |                 |                       | L                          |          | 0x00000000 |

#### Figure 3-1 System address map

Table 3-2 shows the processor interfaces that are addressed by the different memory map regions.

## Table 3-2 Memory regions

| Memory Map    | Region                                                                                                |

|---------------|-------------------------------------------------------------------------------------------------------|

| Code          | Instruction fetches are performed over the ICode bus. Data accesses are performed over the DCode bus. |

| SRAM          | Instruction fetches and data accesses are performed over the system bus.                              |

| SRAM bit-band | Alias region. Data accesses are aliases. Instruction accesses are not aliases.                        |

| Peripheral    | Instruction fetches and data accesses are performed over the system bus.                              |

### Table 3-2 Memory regions (continued)

| Memory Map             | Region                                                                                                                                                                                                                                           |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peripheral bit-band    | Alias region. Data accesses are aliases. Instruction accesses are not aliases.                                                                                                                                                                   |

| External RAM           | Instruction fetches and data accesses are performed over the system bus.                                                                                                                                                                         |

| External Device        | Instruction fetches and data accesses are performed over the system bus.                                                                                                                                                                         |

| Private Peripheral Bus | External and internal <i>Private Peripheral Bus</i> (PPB) interfaces. See <i>Private peripheral bus</i> .<br>This memory region is <i>Execute Never</i> (XN), and so instruction fetches are prohibited. An MPU, if present, cannot change this. |

| System                 | System segment for vendor system peripherals. This memory region is XN, and so instruction fetches are prohibited. An MPU, if present, cannot change this.                                                                                       |

See the *ARMv7-M Architecture Reference Manual* for more information about the memory model.

### 3.4.1 Private peripheral bus

The internal Private Peripheral Bus (PPB) interface provides access to:

- the Instrumentation Trace Macrocell (ITM)

- the Data Watchpoint and Trace (DWT)

- the Flashpatch and Breakpoint (FPB)

- the *System Control Space* (SCS), including the Memory Protection Unit (MPU) and the Nested Vectored Interrupt Controller (NVIC).

The external PPB interface provides access to:

- the *Trace Point Interface Unit* (TPIU)

- the *Embedded Trace Macrocell* (ETM)

- the ROM table

- implementation-specific areas of the PPB memory map.

## 3.4.2 Unaligned accesses that cross regions

The Cortex-M3 processor supports ARMv7 unaligned accesses, and performs all accesses as single, unaligned accesses. They are converted into two or more aligned accesses by the DCode and System bus interfaces.

—— Note ———

All Cortex-M3 external accesses are aligned.

Unaligned support is only available for load/store singles (LDR, STR). Load/store double already supports word aligned accesses, but does not permit other unaligned accesses, and generates a fault if this is attempted.

Unaligned accesses that cross memory map boundaries are architecturally Unpredictable. The processor behavior is boundary dependent, as follows:

• DCode accesses wrap within the region. For example, an unaligned halfword access to the last byte of Code space (0x1FFFFFF) is converted by the DCode interface into a byte access to 0x1FFFFFFF followed by a byte access to 0x00000000.

- System accesses that cross into PPB space do not wrap within System space. For example, an unaligned halfword access to the last byte of System space (0xDFFFFFF) is converted by the System interface into a byte access to 0xDFFFFFFF followed by a byte access to 0xE0000000. 0xE0000000 is not a valid address on the System bus.

- System accesses that cross into Code space do not wrap within System space. For example, an unaligned halfword access to the last byte of System space (0xFFFFFFF) is converted by the System interface into a byte access to 0xFFFFFFFF followed by a byte access to 0x00000000. 0x00000000 is not a valid address on the System bus.

- Unaligned accesses are not supported to PPB space, and so there are no boundary crossing cases for PPB accesses.

Unaligned accesses that cross into the bit-band alias regions are also architecturally Unpredictable. The processor performs the access to the bit-band alias address, but this does not result in a bit-band operation. For example, an unaligned halfword access to 0x21FFFFFF is performed as a byte access to 0x21FFFFFF followed by a byte access to 0x22000000 (the first byte of the bit-band alias).

Unaligned loads that match against a literal comparator in the FPB are not remapped. FPB only remaps aligned addresses.

# 3.5 Write buffer

To prevent bus wait cycles from stalling the processor during data stores, buffered stores to the DCode and System buses go through a one-entry write buffer. If the write buffer is full, subsequent accesses to the bus stall until the write buffer has drained. The write buffer is only used if the bus waits the data phase of the buffered store, otherwise the transaction completes on the bus.

DMB and DSB instructions wait for the write buffer to drain before completing. If an interrupt comes in while DMB or DSB is waiting for the write buffer to drain, the processor returns to the instruction following the DMB or DSB after the interrupt completes. This is because interrupt processing acts as a memory barrier operation.

# 3.6 Exclusive monitor

The Cortex-M3 processor implements a local exclusive monitor. For more information about semaphores and the local exclusive monitor see the *ARMv7M ARM Architecture Reference Manual*.

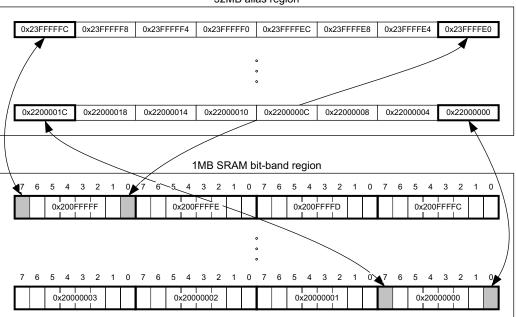

# 3.7 Bit-banding

Bit-banding maps a complete word of memory onto a single bit in the bit-band region. For example, writing to one of the alias words sets or clears the corresponding bit in the bit-band region. This enables every individual bit in the bit-banding region to be directly accessible from a word-aligned address using a single LDR instruction. It also enables individual bits to be toggled without performing a read-modify-write sequence of instructions.

The processor memory map includes two bit-band regions. These occupy the lowest 1MB of the SRAM and Peripheral memory regions respectively. These bit-band regions map each word in an alias region of memory to a bit in a bit-band region of memory.

The System bus interface contains logic that controls bit-band accesses as follows:

- It remaps bit-band alias addresses to the bit-band region.

- For reads, it extracts the requested bit from the read byte, and returns this in the *Least Significant Bit* (LSB) of the read data returned to the core.

- For writes, it converts the write to an atomic read-modify-write operation.

- The processor does not stall during bit-band operations unless it attempts to access the System bus while the bit-band operation is being carried out.

The memory map has two 32-MB alias regions that map to two 1-MB bit-band regions:

- Accesses to the 32-MB SRAM alias region map to the 1-MB SRAM bit-band region.

- Accesses to the 32-MB peripheral alias region map to the 1-MB peripheral bit-band region.

A mapping formula shows how to reference each word in the alias region to a corresponding bit, or target bit, in the bit-band region. The mapping formula is:

```

bit_word_offset = (byte_offset x 32) + (bit_number × 4)

```

bit\_word\_addr = bit\_band\_base + bit\_word\_offset

where:

- bit\_word\_offset is the position of the target bit in the bit-band memory region.

- bit\_word\_addr is the address of the word in the alias memory region that maps to the targeted bit.

- bit\_band\_base is the starting address of the alias region.

- byte\_offset is the number of the byte in the bit-band region that contains the targeted bit.

- bit\_number is the bit position, 0 to 7, of the targeted bit.

Figure 3-2 on page 3-17 shows examples of bit-band mapping between the SRAM bit-band alias region and the SRAM bit-band region:

- The alias word at 0x23FFFFE0 maps to bit [0] of the bit-band byte at 0x200FFFFF: 0x23FFFFE0 = 0x22000000 + (0xFFFFF\*32) + 0\*4.

- The alias word at 0x23FFFFFC maps to bit [7] of the bit-band byte at 0x200FFFFF: 0x23FFFFFC= 0x22000000 + (0xFFFFF\*32) + 7\*4.

- The alias word at 0x22000000 maps to bit [0] of the bit-band byte at 0x20000000: 0x22000000 = 0x22000000 + (0\*32) + 0\*4.

The alias word at 0x2200001C maps to bit [7] of the bit-band byte at 0x20000000: 0x2200001C = 0x22000000 + (0\*32) + 7\*4.

### Figure 3-2 Bit-band mapping

### 3.7.1 Directly accessing an alias region

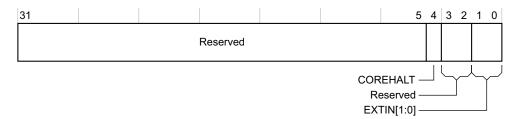

Writing to a word in the alias region has the same effect as a read-modify-write operation on the targeted bit in the bit-band region.